基于FPGA+DSP的光纤数据传输电路设计

赵 喆,张会新,李晓宇,畅彦祥

(1.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051;2.陆军装备部驻北京地区军事代表局某代表室,北京 100042)

随着通信技术的发展,航空航天、武器装备等系统内电子设备越来越多,设备间的硬件配置和控制交互越来越复杂[1],并行I∕O电路消耗硬件资源越来越大,系统数字化、信息化、监听化、实时性要求越来越高[2],使系统内设备的互连线组和数据总量成倍增长,这对系统的信息处理和电路的传输能力提出了更高的要求[3]。因此,需要研究一种具有高速串行、高可靠性、多接口传输的数据传输电路,对设备工作状态、姿态数据、控制指令等进行传输,这对外系统等效器项目研制、试验评估、技术迭代具有重要意义[4]。

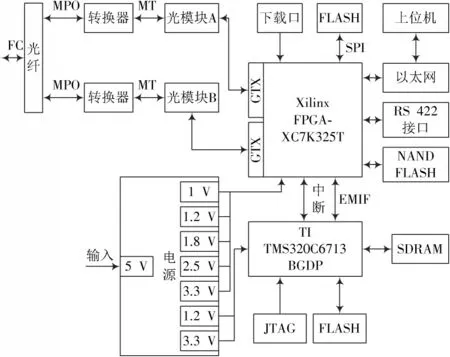

本文针对高速数据传输的要求设计一种光纤数据传输电路,应用于外系统等效器项目。通过4路并行光收发一体模块对多模光纤上的信号进行光电转换,接口转换器提供多种形式光接口与不同测量系统连接进行数据传输;通过FPGA+DSP结构作为核心处理器对数据进行串∕并行收发和交互处理[5],内部封装符合FC-AE-1553总线标准的IP核,通过千兆以太网向计算机传输数据、指令。

1 系统整体设计

明确项目设计要求和电路试验需求,将光纤数据传输电路硬件设计分为6部分,光纤数据传输电路总体框图如图1所示。

图1 光纤数据传输电路总体框图

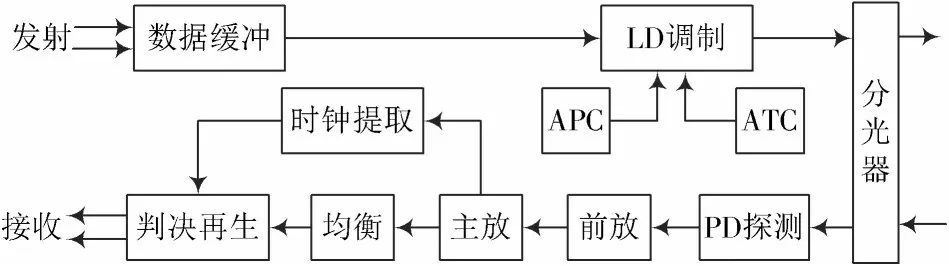

光纤传输采用OM3多模光缆,支端为FC接口,主端为MPO接口;光接口转接器将MPO接口转变为MT接口,光电转换采用两个四路并行光收发一体模块,硬件双冗余可确保数据高可靠性;数据收发采用Xilinx Kintex-7系列FPGA的GTX Bank,125 MHz外部时钟源;数据处理采用FPGA+DSP结构,通过异步通信EMIF总线进行数据交互;数据传输采用千兆以太网与上位机进行指令、数据通信;输入电源提供多种电压,保证各芯片电路顺序上电。传统光纤系统由发射端、光纤、接收端三部分组成。发射端将数据、图像等电信号转为光信号;光纤将光信号传输到接收端;接收端将接收的光信号转为电信号,还原出原信号。传统光纤系统单向传输和体积大限制了应用,而光收发一体模块的出现解决了这一问题,即可以光电、电光转换和独立发射驱动及接收放大[6]。光收发一体模块具有结构小、成本低、可靠性高、性能强等优势[7],结构如图2所示。

图2 光收发一体模块结构图

电路采用模块化设计原则对各功能模块单独设计,最后对整体接口进行优化设计。这样可借鉴已有设计缩短开发周期,节约硬件资源,提高设计效率,便于查错、维护及协助,也能保证电路设计的可靠性、重复使用性和质量保证性等满足要求。

2 硬件电路设计

2.1 FPGA选型

FPGA以并行工作模式提高了数据处理能力,大大缓冲空间从而提高了数据传输能力[8]。FPGA作为光纤数据传输电路的核心芯片,具有开发周期短、开发成本低、接口适应性强、程序移植性强、编程语言简单等优势。电路设计中,FPGA主要负责产生数据、处理数据、传输数据等,因此,需要FPGA具有丰富的高速串行接口、高速存储接口、丰富的内部逻辑资源和I∕O资源、功耗低、尺寸小等特点[9]。Kintex-7系列FPGA在功耗、性能、成本和设计可移植性等方面都取得了重大进展,使FPGA平台能够满足日益多样化的设计群体的需求。本文选型中发现Kintex-7系列FPGA资源适中、性价比高,可满足电路设计要求,最终选择Kintex-7系列FPGA的XC7K325T-FFG900型号。

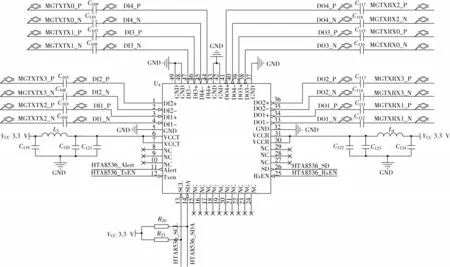

2.2 FPGA外部电路

GTX Bank使用115Quad、118Quad,外部晶振频率为125 MHz,提供给MGTREFCLK0参考时钟差分输入引脚,使用四收四发高速串行数据差分对。MGTAVTTRCAL引脚端接阻抗校准电路供电电源,MGTRREF引脚端接阻抗电路校准阻抗输入,电阻精度优于1%,在配置FPGA期间执行阻抗校准,然后把校准值分发给同列的其他GTX通道。同一列中如果有GTX收发器被用到,则带RCAL主电路的GTX Quad必须正常供电;如果没有使用,这两个引脚都应接地。GTX接口电路如图3所示。

图3 GTX接口电路图

2.3 DSP选型

为满足高精度数据处理和大容量传输,以及电路核心资源数量多的需求,选择一款合适的DSP[10]。考虑DSP的硬件资源、处理速度、运算功耗等因素,并且考虑到浮点型DSP比定点DSP的计算能力强、数据精确度高,更适合高精度复杂数据处理[11]。TMS320C6713B的时钟频率适中、性价比高、满足电路对数据的高速传输要求,因此DSP处理器选择TMS320C6713B型号。

TMS320C6713B是TMS320C6713的升级版本,同属TI公司的TMS320C6000系列,区别在于TMS320C6713B去掉了复位信号的内部上拉电阻,在设计电路时注意加外部上拉或使用电压监测芯片。

2.4 以太网模块

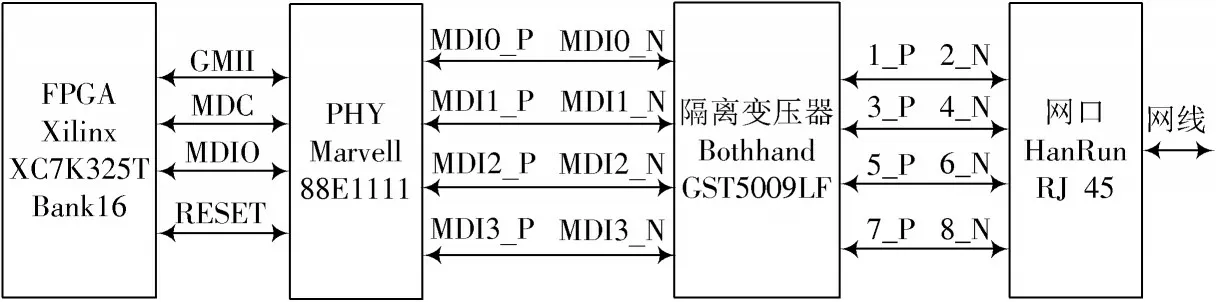

FPGA逻辑编程实现MAC层功能,通过GMII∕RGMII接口实现FPGA与PHY芯片88E1111的衔接;隔离变压器GST5009通过MDI接口实现PHY芯片与RJ 45端子的连接,使用超五类网线连接到计算机。以太网硬件组成图如图4所示。

图4 以太网硬件组成图

2.5 光电转接模块

光电转换功能使用了一款高性能LCC48封装的四路并行光收发一体模块。该模块自带收发光功率、电压、温度监控等功能,通过I2C协议将信息传输给FPGA。模块输出端口为具有一定长度的圆纤,尾部为MT光接口[12]。

光模块接口电路如图5所示。

图5 光模块接口电路图

3 逻辑设计

3.1 数据收发逻辑设计

光信号传输采用双冗余设计,正常情况下由通道A发送数据,当通道A链路不完整时,变为通道B发送数据,因此数据传输电路可靠性提高。接收数据同发送数据一样,接收到数据后判断是否为递增数,以证明电路设计的正确性。数据收发流程如图6所示。

图6 数据收发流程

光纤数据传输电路使用GTX高速串行收发器完成数据的接收和发送。选用XC7K325T型号FPGA的7 Series GTX IP核,使用7 Series FPGAs Transceivers Wizard对配置协议、线速率、参考时钟、数据宽度、编码方式、收发通道等参数进行配置。设置Q0组的X0Y0-X0Y3和Q3组的X0Y12-X0Y15收发通道,配置协议选择start_from_scratch,线速率为2.5 Gb∕s,外部参考时钟为125 MHz,PLL选择CPLL,数据宽度为16位,编码方式为8 B∕10 B。

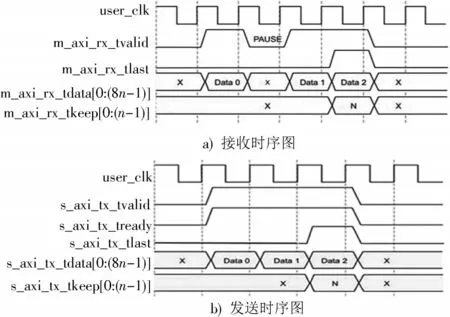

发送端包括:信号源提供给GTX的s_axi_tx_data数据帧、s_axi_tx_tkeep指示在最后字节中有效位长度、s_axi_tx_tlast指示最后字节位置、s_axi_tx_tvalid指示有效字节位置的3个控制信号,以及GTX接口反馈的s_axi_tx_tready指示数据。接收端有与发送端相对应的m_axi_tx_data、m_axi_tx_tvalid、m axi tx last、maxi_tx_tkeep四个信号。由于接收端没有内置弹性缓冲区,因此没有与s_axi_tx_tready相对应的信号。接收和发送时序图如图7所示。

图7 接收和发送时序图

FPGA与DSP间实现数据收发通信是电路难点,为解决两者的通信接口问题,采用EMIF总线+中断响应方式实现双向传输。本文电路将FPGA内部的块存储器配置为真正双口RAM用于访问共享的存储空间,每个端口的数据线、地址线、读写控制线可以允许不同系统同时对共享存储区进行访问。

使用DSP系统和FPGA系统进行访问,SP通过EMIF总线访问FPGA内部双口RAM的A端口,FPGA访问双口RAM的B端口。EMIF数据线通过选择器连接到A端口的数据输入输出端口,由中断控制线时数据传输方向进行控制。

3.2 以太网逻辑设计

以太网实现电路与上位机通信,完成FPGA中寄存器配置、传输指令下发和数据回读。本文电路在FPGA内实现UDP协议和ARP协议,以完成以太网通信。UDP协议属于传输层,ARP协议属于网络层。以太网标准划分为应用层、传输层、网络层、数据链路层、物理层等5层。一帧数据包由前导码、SFD、以太网帧头、数据段、FCS、IFG组成。数据包格式如图8所示。

图8 以太网数据包格式

协议表示携带的数据是何种协议,01代表ICMP,06代表TCP,17代表UDP,本文电路使用“0x11”。源IP地址代表发送端的IP地址,本文电路使用192.168.12.2;目的IP地址代表接收端的IP地址,本文电路使用192.168.12.3。数据链路层负责接收网络层的IP数据包封装成帧送到物理层传输,或者从网络上接收物理帧并抽出IP数据包交给网络层。

4 实验结果

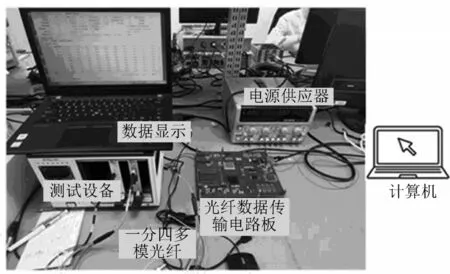

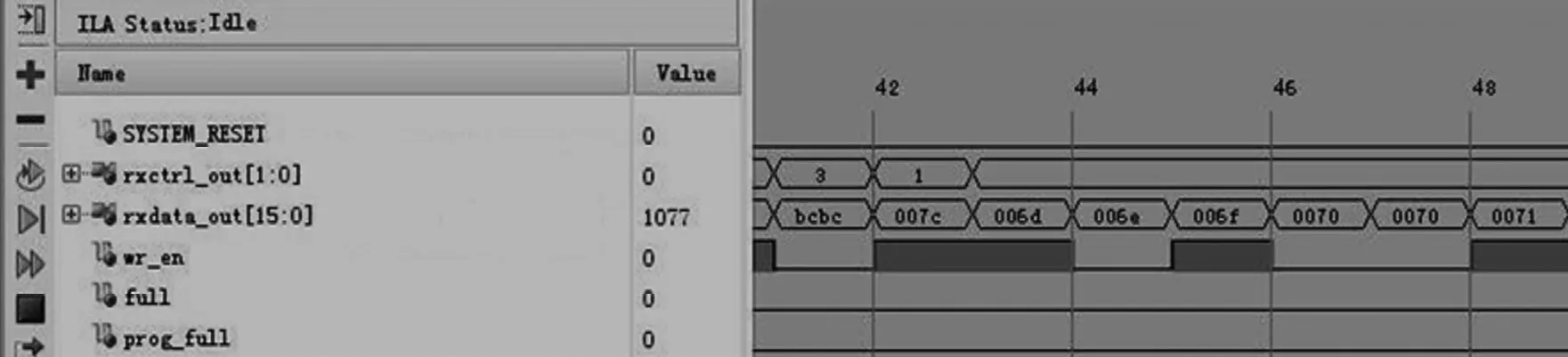

光纤数据传输电路作为外系统等效器中不可或缺的一部分,由光纤数据传输电路板、电源供应器、计算机、采集板卡、多模光纤线缆组成。本文搭建硬件平台进行实验测试,搭建完成后的测试电路实物图如图9所示。GTX Bank进行回环测试以确保可正常工作。本文电路选择近端PCS回环。发送端数据如图10所示,接收端数据如图11所示。在发送端口输出模拟数据,其中“0xbcbc”和“0x007c”为帧标志,在接收端口接收数据并比较一致性。结果显示数据基本一致,但存在相位差,表明GTX Bank可以正常工作。

图9 测试电路实物图

图10 发送端数据图

图11 接收端数据图

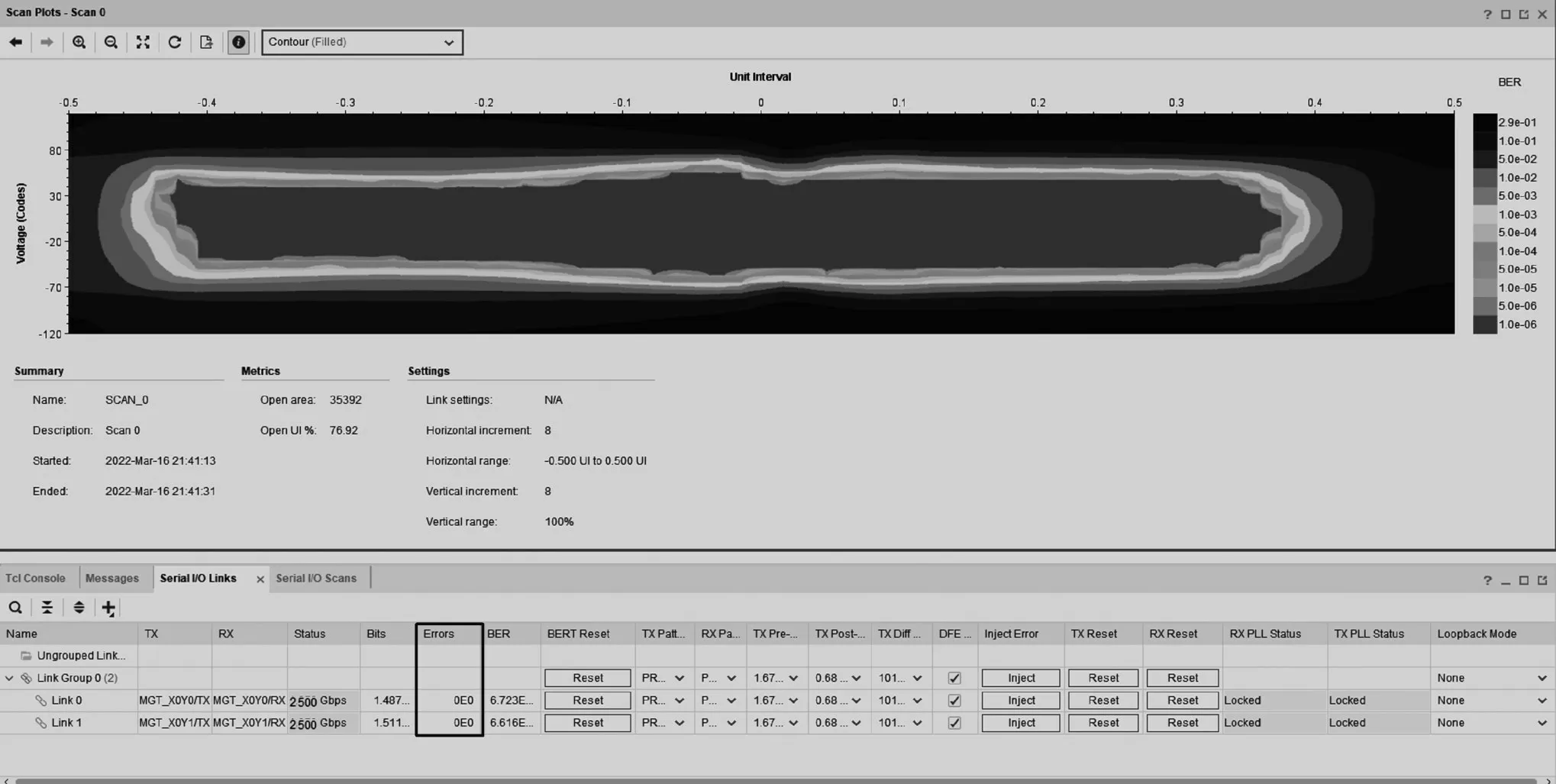

使用Vivado自带的IBERT 7 Series GTX进行眼图测试,选择线速率为2.5 Gb∕s,参考时钟为125 MHz。经过一段时间数据测试,Errors一直显示为0,表明测试过程稳定能够在线速率2.5 Gb∕s下进行数据传输。测试结果如图12所示。

图12 2.5 Gb/s眼图测试结果

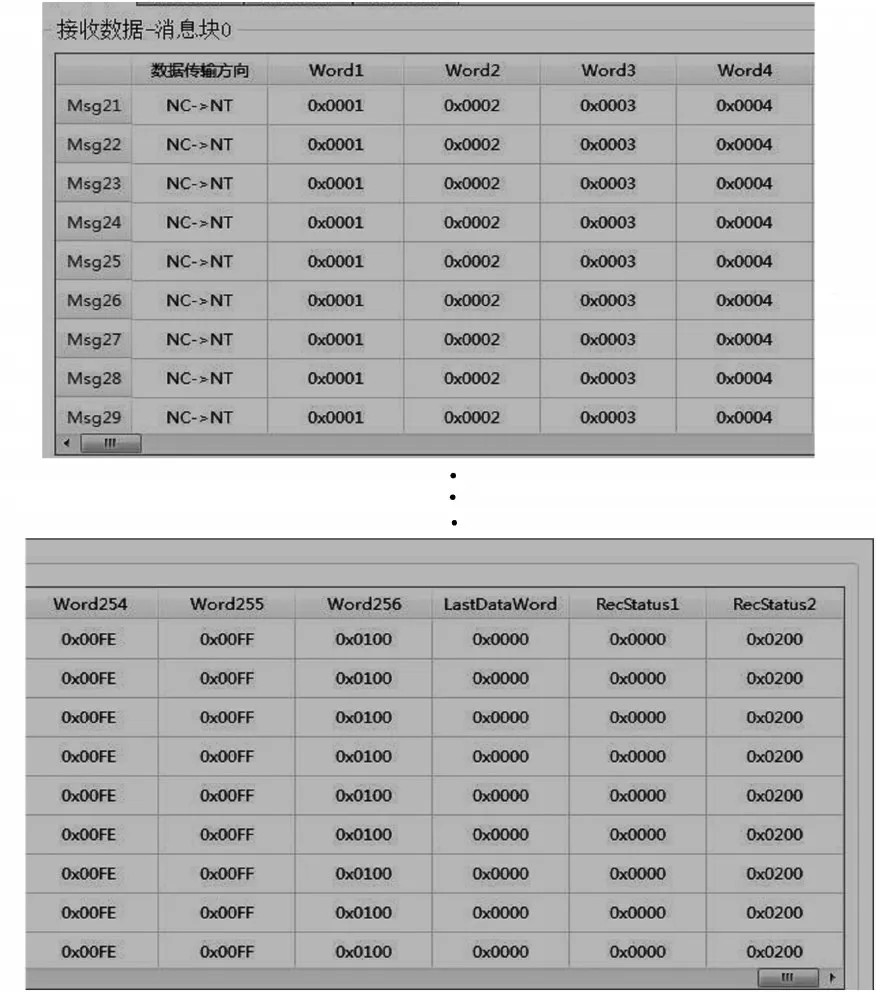

电路上电后整体复位并将寄存器清零,读取硬件光纤的连接状态(正常为0x07,异常为0x408),配置站点类型、ID号,NC、NT功能初始化,开始循环发送数据。数据接收结果如图13所示。计算机的IP地址设为192.168.12.3,MAC地址为0x94C69177828B,光纤数据传输电路板IP地址设为192.168.12.2,MAC地址为0x000A3501FEC0,两者通过网线连接。

图13 数据接收结果图

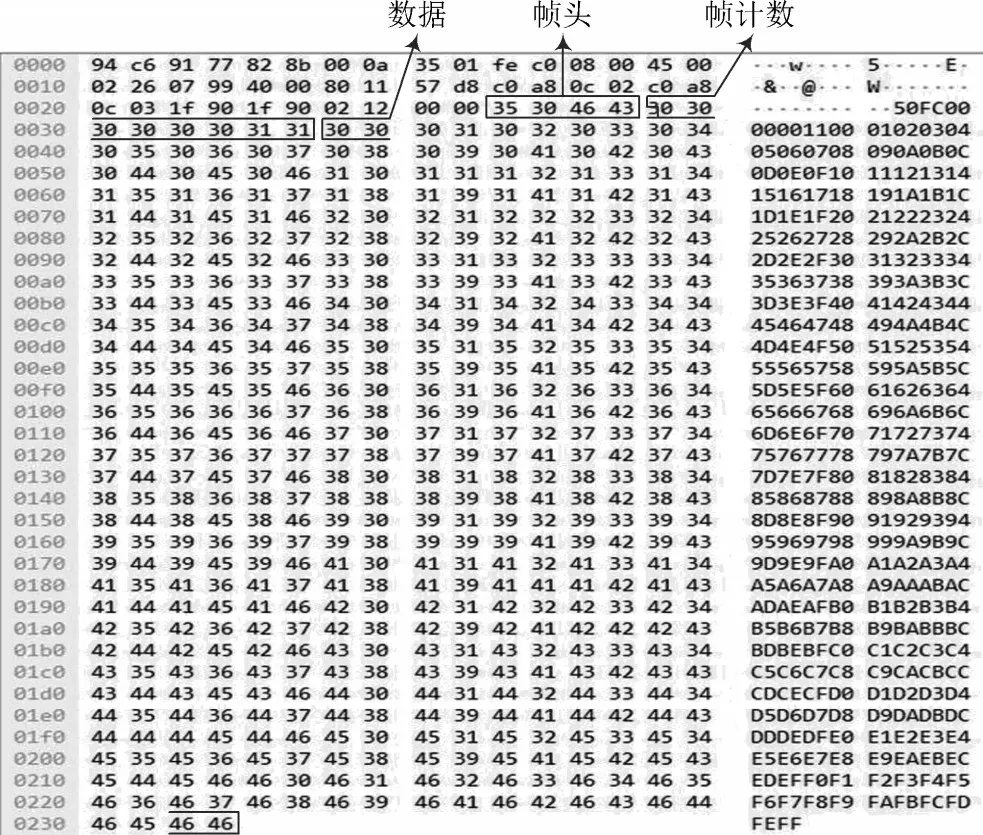

FPGA给上位机传输数据,其中0x50FC为帧头,0x00000011为包计数,其余为数据。

以太网数据传输结果如图14所示。

图14 以太网传输数据结果

5 结 论

本文依据外系统等效器项目设计要求和电路试验需求,对光纤数据传输电路现状进行了深入研究,设计了一种基于FPGA+DSP的光纤数据传输电路。电路采取模块化设计,详细解释了其数据传输方式,搭建测试系统完成了FPGA与DSP之间实时的数据处理以及千兆以太网上位机通信,实现了数据的高速交互,为大容量数据高速传输提供了新的参考方向。