矢量信号分析中高性能模拟信号采集系统的研究

陈慧娟,游 政,张立佳,程景清

(南京洛普科技有限公司,江苏 南京 210032)

0 引 言

现代通信中融合了大量先进技术,这要求与之相关的电子测量仪器具备宽带、实时矢量信号捕捉和分析能力。中频数字化技术是实现这一过程的先进技术手段。本文研究基于某型号便携式矢量信号分析仪,频率范围高达8 GHz;分析仪采用的信号处理方法是模拟超外差下变频和数字中频处理技术。数字中频是采用模拟信号采集系统将模拟中频信号变换为数字中频信号,再进行数字信号处理,如数字下变频(DDC)、数字抽取和滤波、数字检波及FFT算法等,实现宽带、实时信号分析。分析项包括频率误差、载波泄漏、正交误差、调制精度、失真测量等,通过矢量分析,用户能快速评估各种模拟和数字通信系统。

全文对于便携式矢量信号分析仪(VSA)的重要组成之一,即高速、高分辨率的模拟信号采集系统进行研究,致力于增大模拟矢量信号的带宽(MHz以上),信号动态范围(100 dB以上),获得更好的信噪比(70 dB以上)。模拟信号占用更宽的带宽意味着要采用高采样率的模数变换器(ADC);更大的动态范围以及更好的信噪比意味着不仅要采用高分辨率的ADC,还要采用高稳定度的采样时钟。整个系统还必须有很好的电磁兼容性设计。全数字中频信号处理要求ADC能高速采样且高分辨率,ADC的性能将直接决定方案的可行性。而目前市场能满足要求的ADC种类稀少并且价格高昂,所以本文中的系统采用自适应技术设计了一种逻辑电路,提高了ADC分辨率,从而解决了这一难题。

1 总体设计方案

模拟中频信号频率范围、模拟中频信号动态范围与接收机信噪比(SNR)三项指标是本文项目中模拟信号采集系统的难点,需要重点分析研究。其中,模拟中频信号频率范围和模拟中频信号动态范围两项决定了模拟抗混叠带通滤波器的设计难度和ADC采样频率的选择;而接收机信噪比(SNR)决定了ADC采样频率源的质量。

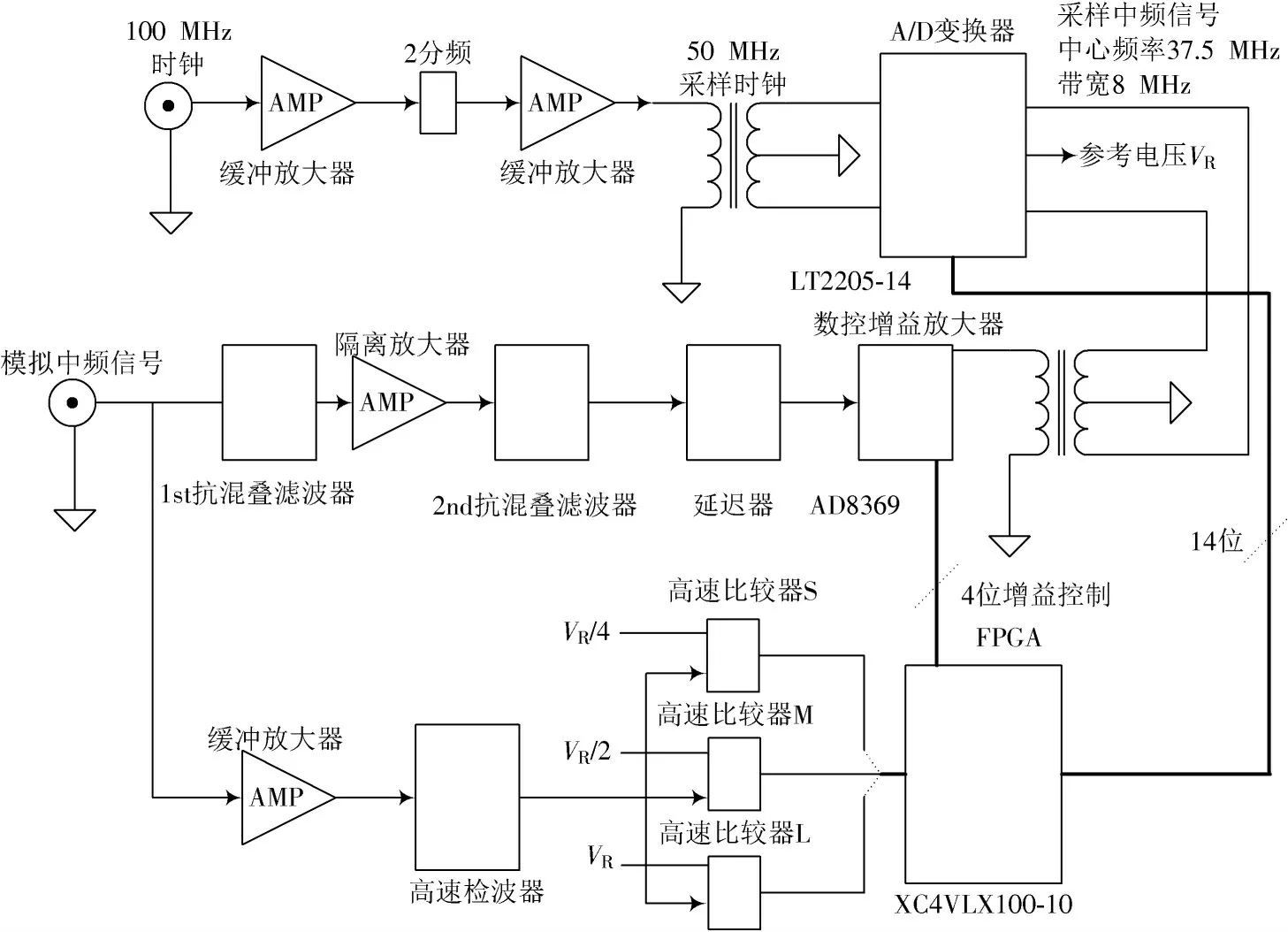

本文模拟信号采集系统的总体设计方案如图1所示。

图1 模拟信号采集系统的设计框图

1.1 经典采样理论与系统前端模拟抗混叠带通滤波器设计

1.1.1 经典采样理论回顾

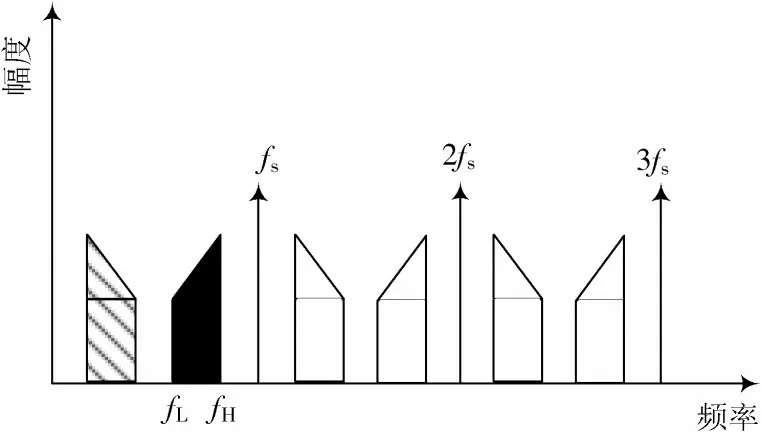

根据Nyquist采样定理,若要从相等时间间隔取得的采样点中,毫无失真地恢复出原模拟信号波形,则要求采样频率fs≥模拟信号中最高频率分量的2倍(过采样),被采样信号的频域分布如图2所示。

图2 被采样信号频谱图

图2中黑色区域为被采样信号的频域分布,方块部分为采样后的数字信号的频域分布,可以看出原信号被搬移到不同的频域。

另一方面,如果模拟信号的带宽小于fs/ 2(f s /2又称Nyquist带宽),那么有可能用低于Nyquist采样准则所要求的采样率进行采样,所需的最小采样频率实际上与输入信号带宽相关,并取决于最大频率成分。

Shannon定理指出,一个带宽为B的模拟信号,采样速率fs必须大于2B,才能避免信息的丢失;而且被采样的信号不能是fs/ 2的整数倍,以防止混叠成分的相互重叠。若信号带宽从fL到fH,而fH-fL=B,则称为欠采样或带通采样。欠采样后的频域分布如图3所示。

图3 欠采样频谱图

图3中黑色区域为被采样信号的频域分布,方块部分为采样后的数字信号的频域分布,可以看出原信号被搬移到不同的频域。由于采样时钟包含谐波(fs,2fs…),故数字中频信号在采样时钟的每一个谐波附近都产生混叠,其中斜线部分的频率最低。

将两种采样方式后的数字信号的频域分布相比较,可以得出以下的结论:

1)采用过采样方式。由于采样时钟fs频率高,混叠成分频率也高,采用容易设计的低通滤波器可以很好地处理采样前的模拟中频信号。缺点是由于采样频率高,在同等技术指标的条件下,对采样时钟的抖动提出了更高的要求;另一方面,采用高采样率的ADC,其信噪比、动态范围、功耗及性价比等多项指标均差于低采样率的ADC。

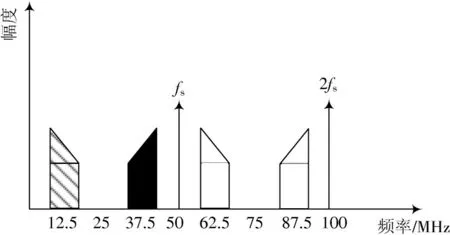

2)采用欠采样方式。由于采样时钟fs频率低,同样指标的采样时钟抖动可以实现更好的信噪比(SNR),其动态范围、功耗及性价比等多项指标均优于高采样率的ADC。缺点是由于混叠成分频率较低(相当靠近有用信号频率),对模拟前端的抗混叠带通滤波器提出了更高的要求。假设模拟中频信号频率为37.5 MHz,信号带宽为10 MHz,ADC采样率fs为50 MHz,要求设计的最大分辨率带宽为3 MHz,无虚假响应动态范围要求达到100 d B,则模拟前端的抗混叠带通滤波器需要在25 MHz,50 MHz和75 MHz等处(3 MHz带宽内)至少抑制110 dB以上才能达到设计要求。采样后的信号频谱如图4所示。

图4 本文采样频谱图

1.1.2 模拟抗混叠带通滤波器的ADS设计与优化

根据频率范围的要求,模拟抗混叠带通滤波器采用LC滤波器设计,中心频率为37.5 MHz,0.1 dB带宽为8 MHz,1 dB带宽为10 MHz;在25 MHz,50 MHz和75 MHz等处(3 MHz带宽内)最大衰减要达到110 dB以上,即矩形系数要达到1∶3以上(B3dB/B110dB<1∶3)。

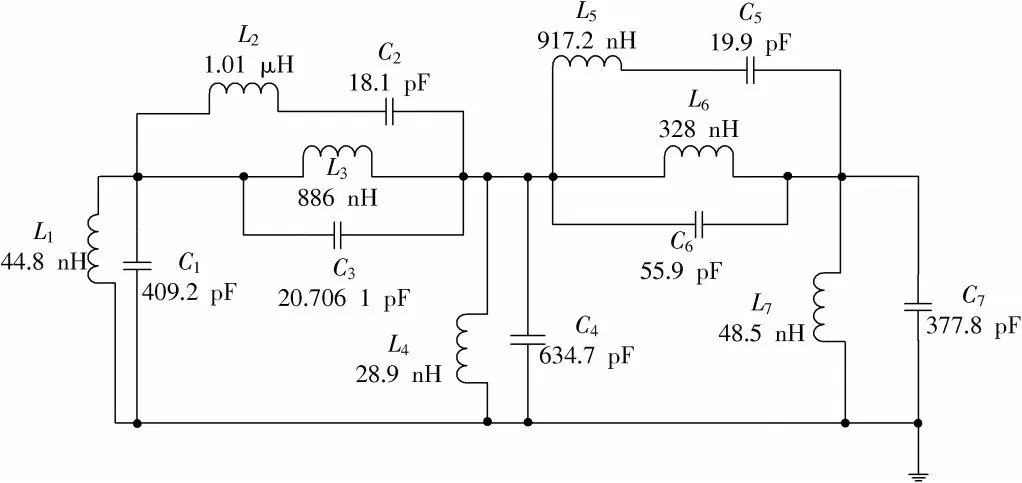

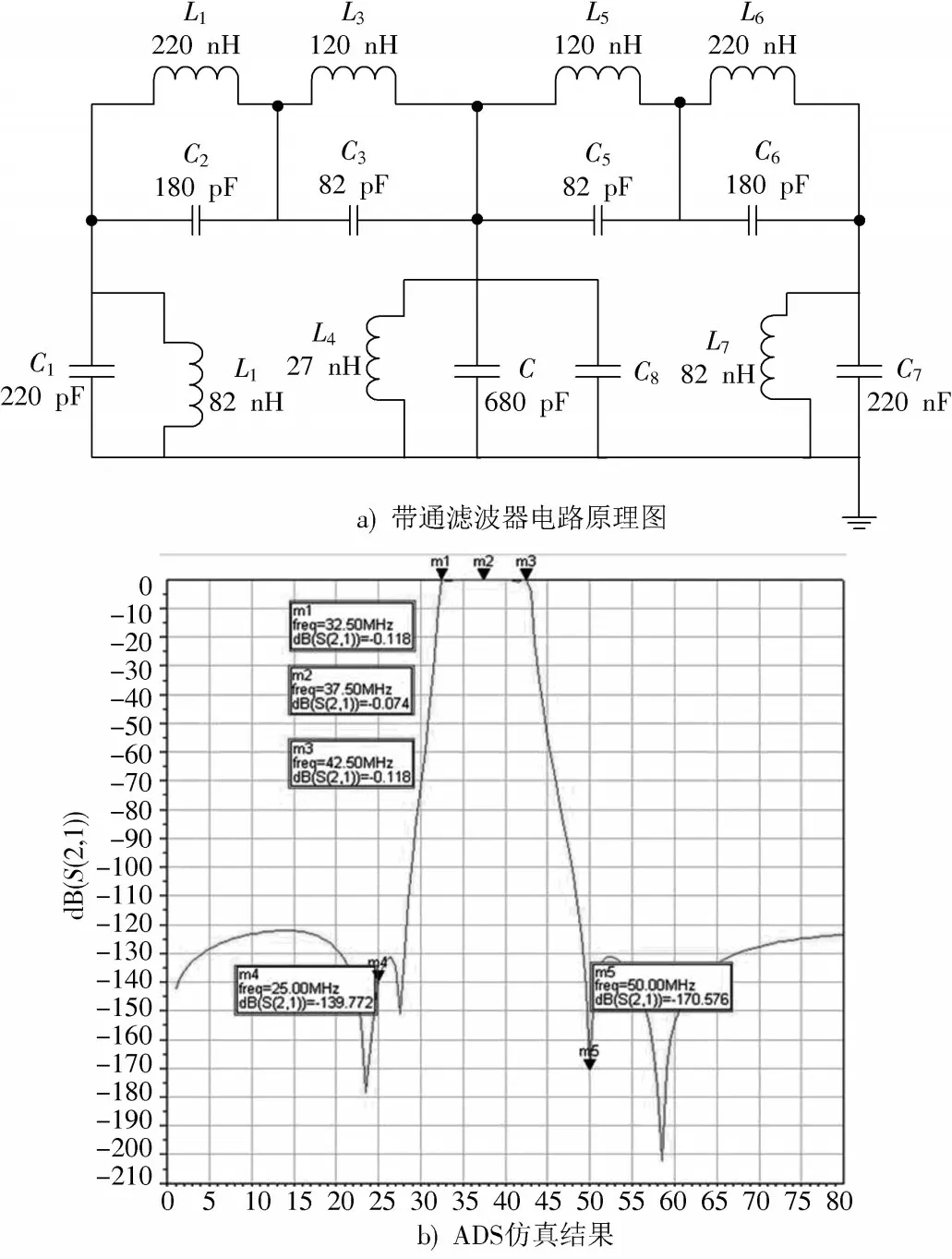

根据上述要求,应用ADS软件进行仿真设计。首先选择滤波器类型。根据矩形系数的要求应当选择椭圆函数带通滤波器(因为其带外衰减最快)。将滤波器的主要参数导入ADS中的滤波器设计模板,得到抗混叠带通滤波器的基本电路,如图5所示。

图5的基本电路在实践中难以应用,其原因为:

图5 5阶椭圆函数带通滤波器电路原理图

1)椭圆函数带通滤波器对元件数值要求相当精确(尤其是通带内的平坦度指标,本文要求较高),而通过ADS软件仿真设计的电路,其元件参数难以具体实现(大量采用可调电感和可调电容又使得电路的体积增大,不符合便携式仪器的要求)。

2)图5所示的椭圆函数带通滤波器电路复杂,尤其是串联支路中谐振回路互相影响(谐振点不能独立设计与调试),实践中造成滤波器性能下降,不能达到本文对带通滤波器的技术指标要求。

根据上述情况,对滤波器电路进行优化,优化的目标如下:

1)在保证滤波器性能指标的前提下,全部采用商品化表面贴装器件(SMD);

2)在保证滤波器性能指标的前提下,尽量采用标准系列的元件(为了减小体积,不采用可调元件)。

优化的方法依据滤波器的诺顿等效变换原理,将图5的电路变换为图6a)的电路,图6a)中,3个并联支路的谐振频率均为带通滤波器的中心频率37.5 MHz;图5中的串联支路变换为图6a)的2个并联回路,它们分别谐振于25 MHz和50 MHz,这是2个衰减极点,对应于带通滤波器的2个最大衰减点。变换过程的计算较为繁琐,此处省略(可参看文献[1])。优化的结果为:实际抗混叠带通滤波器由2组5阶椭圆函数带通滤波器级联构成,这2组滤波器的形式完全相同,中间经过放大器隔离。为了保证级联后的滤波器性能良好,对隔离放大器的S参数进行了仿真设计。优化后的5阶椭圆函数带通滤波器电路原理图及ADS仿真结果如图6所示,限于篇幅,只给出1组滤波器的电路原理图及级联后的实际抗混叠带通滤波器的ADS仿真结果。

图6 优化后的5阶椭圆函数带通滤波器电路原理图及ADS仿真结果

1.2 采样时钟频率、抖动与相位噪声

1.2.1 采样时钟频率设计

采用欠采样的技术带来的一个缺点是会产生更多的混叠分量。由于采样时钟包含谐波(fs,2fs,…),模拟中频信号在采样时钟的每一个谐波附近都产生混叠。分析图2中采样信号的频域分布不难看出,为了防止混叠成分互相重叠,采样时钟的频率fs应满足如下关系式:

式中,n为大于1而小于INT(fL/fH-fL)之间的整数。

根据本文要求,将fL=32.5 MHz,fH=42.5 MHz代入,可知n小于4。当n=l时,41.5 MHz≤fs≤67 MHz;当n=2时,27.7 MHz≤fs≤33.5 MHz;当n=3时,20.75 MHz≤fs≤22.3 MHz;当n=4时,16.6 MHz≤fs≤16.75 MHz。容易看出,n取1时,对抗混叠带通滤波器的矩形系数要求最低。据此,本文选取fs为50 MHz。从图4可以看出,欠采样后原模拟信号频谱分别搬移至中心频率为12.5 MHz,62.5 MHz,87.5 MHz等处,其中任何一个混叠成分都是原始信号的一个准确描述。为了方便起见,后续数字电路处理的是中心频率为12.5 MHz的混叠分量。

1.2.2 采样时钟抖动对高速ADC信噪比的影响

高速ADC的动态特性的最大弊端在于采样抖动(Jitter),包括采样保持电路的孔径抖动和采样时钟的抖动,而输入模拟信号频率较高时,采样时钟抖动将占据主导地位。由于抖动造成采样时刻的不确定性,因而带来了采样误差,导致数字量化后幅度的不确定性。这种不确定性导致ADC可重复性大大降低,而可重复性决定ADC的频域性能,因此,高速ADC的频域性能受Jitter影响是非常大的。

根据本文要求对模拟中频信号进行高速采样的ADC有效位数需要14位,采样时钟为50 MHz,模拟中频信号上限频率fH为42.5 MHz,需要的信噪比(SNR)大于76 dB。据此进行采样时钟设计。

1)根据经典公式计算抖动(Jitter)的大小,SNR(单位为dB)公式为:

可以计算Jitter的大小应该符合:

将fH为42.5 MHz,SNR为76 dB代入式(3)可得Jitter约为594fs,这是总Jitter。而总Jitter由两项构成,可以由下式计算:

式中:第一项为ADC本身采样保持电路的孔径抖动,常用的14位高速ADC芯片本身采样保持电路的孔径抖动小于100fs(14位ADCLTC2205-14为80fs);第二项为采样时钟的抖动,其大小为:

由式(5)可知,为了满足大动态范围和优良的信噪比要求的高速ADC,需要精心选择采样时钟信号。通常采样时钟信号是由晶体振荡器提供,而市场上常用的普通晶体振荡器往往不能满足要求。举例来说,若采用市场上常用的50 MHz晶体振荡器(非温度补偿),其时钟抖动约为1.5 ps,输入模拟中频信号为42.5 MHz,依然采用14位ADCLTC2205-14(芯片采样抖动为80fs),将有关数据代入,计算后得到SNR约为62 dB,只相当于10位的ADC。

以上分析说明,为了满足14位ADC的要求,需要精心选择采样时钟信号。下文根据时钟抖动的要求研究晶体振荡器的技术指标。

晶体振荡器的频率指标包括频率标称值、长期稳定度和短期稳定度。长期稳定度一般定义为日稳定度和年老化率,短期稳定度一般由相位噪声定义。很明显,时钟抖动属于时域短期稳定度范畴。相位噪声为频域,定义为功率谱密度,单位为dBc∕Hz,与时钟抖动的单位没有明显的换算关系。

1.2.3 根据采样时钟抖动计算相位噪声

根据已发表的资料(可参看参考文献[2]),采样时钟的相位噪声功率谱密度clkSD与采样时钟频率fs、ADC采样时钟带宽clkBW、模拟中频信号最高频率fH和采样时钟抖动tJitter的关系式为:

根据式(6)也可以求解时钟抖动,关系式为:

根据以上分析,本文项目选择信息产业部第13研究所生产的100 MHz恒温晶体振荡器,型号为OX36-100M,二分频后(50 MHz)作为ADC采样时钟fs。该晶体振荡器的近端相位噪声指标为-150 dBc∕Hz(1 kHz偏移),二分频后为-156 dBc∕Hz(1 kHz偏移)。选用mini-circuit公司的平衡变压器TC4-1W+(带宽clkBW为400 MHz)作为ADC时钟驱动电路,将数值代入式(7)得到tJitter(单位为s):

计算出来的时钟抖动tRMS约为383fs,远小于式(5)中的588fs,符合对时钟驱动的抖动要求。

1.3 自适应技术在高速、高分辨率ADC电路中的应用

ADC是数字系统的重要单元,尤其是在全数字中频信号处理中,它的性能直接决定了整个方案的可行性。ADC的有效位数决定了显示动态范围,ADC的信噪比决定了显示噪声水平,ADC的量化非线性可能造成寄生分量等。由于是在模拟中频信号上直接进行采样,中频频率一般在几十MHz,无论采用哪一种采样技术,需要的采样速率都高达几十MHz以上。另外,ADC的有效位数B与显示动态范围D(单位为dB)有如下关系:

如果需要显示动态范围大于100 dB,则ADC的有效位数至少达到16位。实际上,全数字中频信号处理对ADC提出了高分辨率和高速采样的双重要求。目前,能达到这种要求的商用ADC品种稀少,且价格相当昂贵。本文采用自适应ADC技术,原理图如图7所示。

前文提及,抗混叠带通滤波器通常由高阶带通滤波器构成,而且其幅频特性曲线相当陡峭,根据滤波器的一般理论,其群时延较大。采用矢量网络分析仪测量本文的两级抗混叠带通滤波器,其群时延大于100 ns,也就是说,射频信号下变频到中频频率后(即图7中的模拟中频信号),通过抗混叠带通滤波器的时间至少需要100 ns。这个延迟时间使较大的模拟中频信号在ADC过载前被高速检波器提前识别出来,然后通过自适应逻辑电路降低ADC前步进增益放大器的增益。通过这项技术可以自动改变ADC前端的放大器增益。如果信号幅度较小,自适应逻辑电路将增大放大器增益,以减小输入端的噪声影响,ADC后的FPGA将记录增益变化并以数字增益加以补偿。这种自适应技术大大提高了扫频模式下ADC的有效位数,提高了ADC的动态范围。实验结果证明,采用了自适应ADC的技术后,ADC的有效位数提高到17位,很好地解决了ADC中高分辨率和高采样率的矛盾。

图7 自适应ADC原理图

1.4 ADC芯片选择

本文综合考虑了ADC的采样率、有效位数、功耗及价格等多方面因素,选择了欠采样方式。采用Linear公司的高速ADC芯片(LTC2205-14),设计采样时钟为50 MHz,对模拟中频信号进行高速采样。LTC2205-14主要技术指标如下:

1)分辨率为14 bit;

2)最大采样率为65 MHz;

3)ADC信噪比(SNR)为77.3 dB;

4)最大动态范围(70 MHz模拟输入)为94 dBc;

5)采样保持电路孔径抖动为80fs;

6)前端程控增益放大器;

7)选件Dither功能。

1.5 其他重要模拟电路设计

本文采用Analog Devices公司的数字控制增益放大器AD8369作为步进增益控制器件,设计时将其配置为三档,分别为6 dB步进、12 dB步进和18 dB步进,分别对应放大倍数的2倍、4倍和8倍。自行设计的高速峰值电压检波器检测输入模拟中频信号的电压幅度,经适当放大后与预先设定的参考电压进行比较。由于要将ADC的有效位数扩大3位,所以专门设计了3组并行高速电压比较器,各组的参考电压分别为VR,VR2和VR/4,比较的结果送自适应数字逻辑电路进行处理。自适应数字逻辑电路在高速FPGA里实现,FPGA根据3组高速电压比较器输出结果的不同组合,产生相应的控制代码控制AD8369的增益,并将这些代码和ADC的转换结果作为ADC的组合输出。

2 系统仿真结果(应用结果)与结果分析

2.1 主要技术指标

通过测试,得到模拟信号采集系统的主要技术指标如下:

1)模拟中频信号频率范围为32.5~42.5 MHz,1 dB带宽为10 MHz;

2)模拟中频信号动态范围>92 dB;

3)接收机信噪比(SNR)>76 dB。

其他指标省略。

2.2 计算总响应时间

自适应ADC技术需要仔细评估各电路的响应时间是否小于两级抗混叠带通滤波器的群时延。根据芯片资料及测量结果可知,AD8369增益控制响应时间约为30 ns,高速峰值检波器和高速电压比较器总的响应时间约为30 ns,FPGA控制时间约为20 ns,总的控制响应时间约为80 ns。预留20 ns的富裕量,实际控制时间约为100 ns,几乎与两级抗混叠带通滤波器的群时延相当。为了增加测量结果的可靠性,在抗混叠带通滤波器后增加了一个时延环节,将模拟中频信号再延迟20 ns,这样很好地保证了扫频模式下测量结果的正确性。

3 结 论

本文针对矢量信号分析仪中最重要的组成之一,即中频模拟信号采集系统进行了深入探讨,主要包括以下几个方面:

1)根据数字中频接收机对模拟信号动态范围及假响应和失真的要求,研究模拟抗混叠带通滤波器的技术指标和实现方法;通过ADS仿真软件进行设计;在此基础上应用网络变换原理进行优化,实现了采用SMD器件设计的高阶抗混叠带通滤波器。

2)根据数字中频接收机对信噪比的要求,研究采样时钟抖动对高速ADC信噪比的影响;推导了信噪比(SNR)与采样时钟抖动的相互关系;分析了采样时钟在频域中的相位噪声指标与时域中的时钟抖动换算关系,在此基础上对本文中采用的100 MHz恒温晶体振荡器进行了时钟抖动计算。

3)研究了自适应技术在高速ADC中的应用,通过对模拟高阶抗混叠带通滤波器的群时延分析和测试,应用自适应技术设计了一种提高ADC分辨率的电路;结合高速检波器、高速电压比较器、数字控制可变增益放大器和FPGA的应用,将高速ADC的有效位数提高了3位,很好地解决了高速ADC中高分辨率和高采样率的矛盾。在此基础上,对本文设计方案仔细加以说明。

综上所述,通过文中各种先进技术的应用,很好地完成了设计目标,设计的数字中频模块(平台)不仅能够应用于某型号便携式矢量信号分析仪,还可以应用于各种民用(尤其是军用)射频测控设备。