FPGA分布式系统的固件升级设计

周云松,黄维雄,刘骁知,范晋文

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

在进行单板FPGA子系统调试时,只需要连接联合测试工作组(JTAG)接口即可完成比特流的加载、在线观测、Flash配置文件的固化等操作,非常便利[1]。然而,当一个系统中有上百个FPGA子系统需要同时加载比特流进行调试时,使用JTAG将变得力不从心[2]。目前军用系统对大规模FPGA系统的固件升级常常使用自定义的通信协议,不同的设备要求不同,不具备通用性[3]。同时部分升级系统只侧重网络上单个FPGA固件升级设计的实现,规避应用环境中使用JTAG升级的安全风险,未有在高速通信系统中应用的案例[4],且不具备升级的灵活性。本文提出的固件升级系统结合了当前较为成熟的技术解决方案,以万兆以太网[5]、TCP/IP协议为基石,解决了通用性问题,在作为系统级的固件升级方案的同时又能作为系统级的通信方案,保证了高速实时通信。系统中还使用了高性能DSP作为系统的主处理器[6],所以整个系统适用于对数据吞吐量和处理性能要求都较高的系统。

2 硬件体系结构

2.1 子系统硬件体系结构

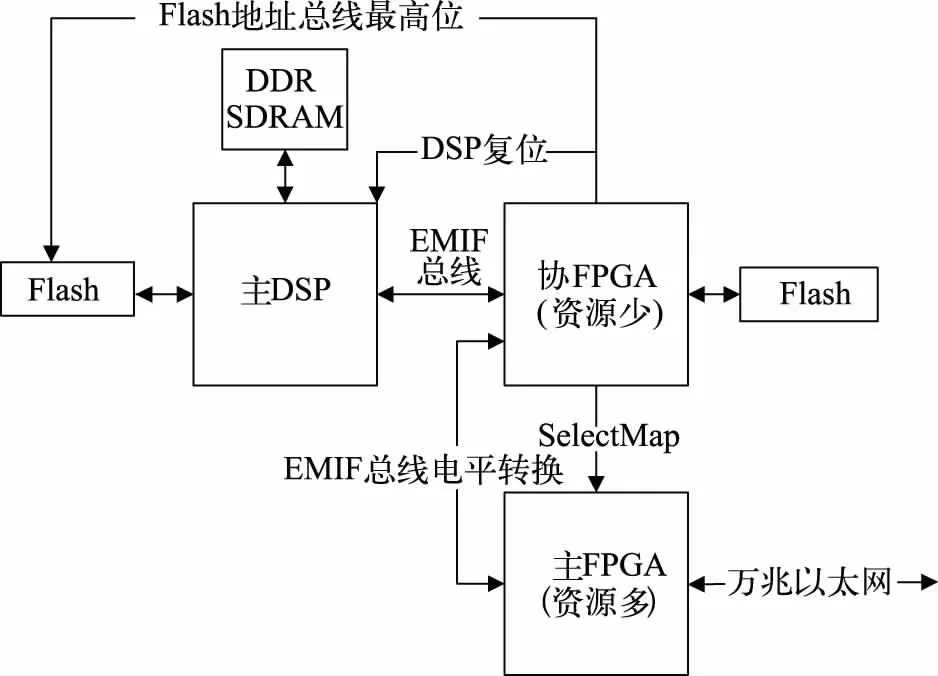

子系统硬件框图如图1所示,框图中只给出了与固件升级相关的硬件连接关系,其余与应用相关的外设连接关系不予讨论。该子系统是典型的DSP+FPGA构架,对系统中主要器件以及连接关系进行简要说明,同样与应用相关的作用也不予讨论。

图1 子系统硬件框图

主处理器DSP型号为TMS320S6455,在固件进行升级操作时从外部存储器接口(EMIF)总线读取固件数据,并存储到Flash中,在子系统上电启动时,将Flash中的固件数据发送至EMIF总线,协FPGA总线通过SelectMap驱动将EMIF固件数据发送至主FPGA,达到启动主FPGA的目的。

主FPGA型号为XC7V690T,为子系统提供万兆以太网的组网能力。协FPGA主要完成系统的状态监控、异常处理、接口驱动、电平转换等功能,这里对电平转换功能进行必要的描述。主DSP的EMIF总线工作电平为3.3 V,而主FPGA为高性能FPGA,其I/O电平只能支持1.8 V,所以二者不能直接相连,必须经过电平转换。由于EMIF总线的I/O数多,需要使用多片电平转换芯片,电路占用面积大,这里巧妙利用了协FPGA支持多种I/O电平的特点,在完成子系统其他功能的同时,使用剩余的I/O管脚,完成了EMIF总线电平转换的功能。

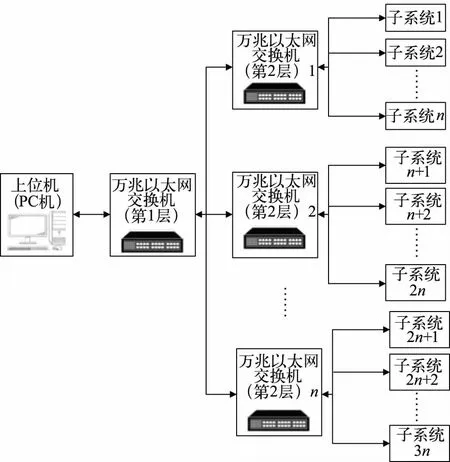

2.2 系统级硬件体系结构

系统级硬件框图如图2所示,该系统由PC上位机、万兆以太网交换机与子系统构成,在进行系统联调或维护升级时,可通过上位机对所有子系统固件进行一键升级,同时上位机可实时查看每一个子系统的状态。

图2 系统级硬件框图

3 软件系统结构

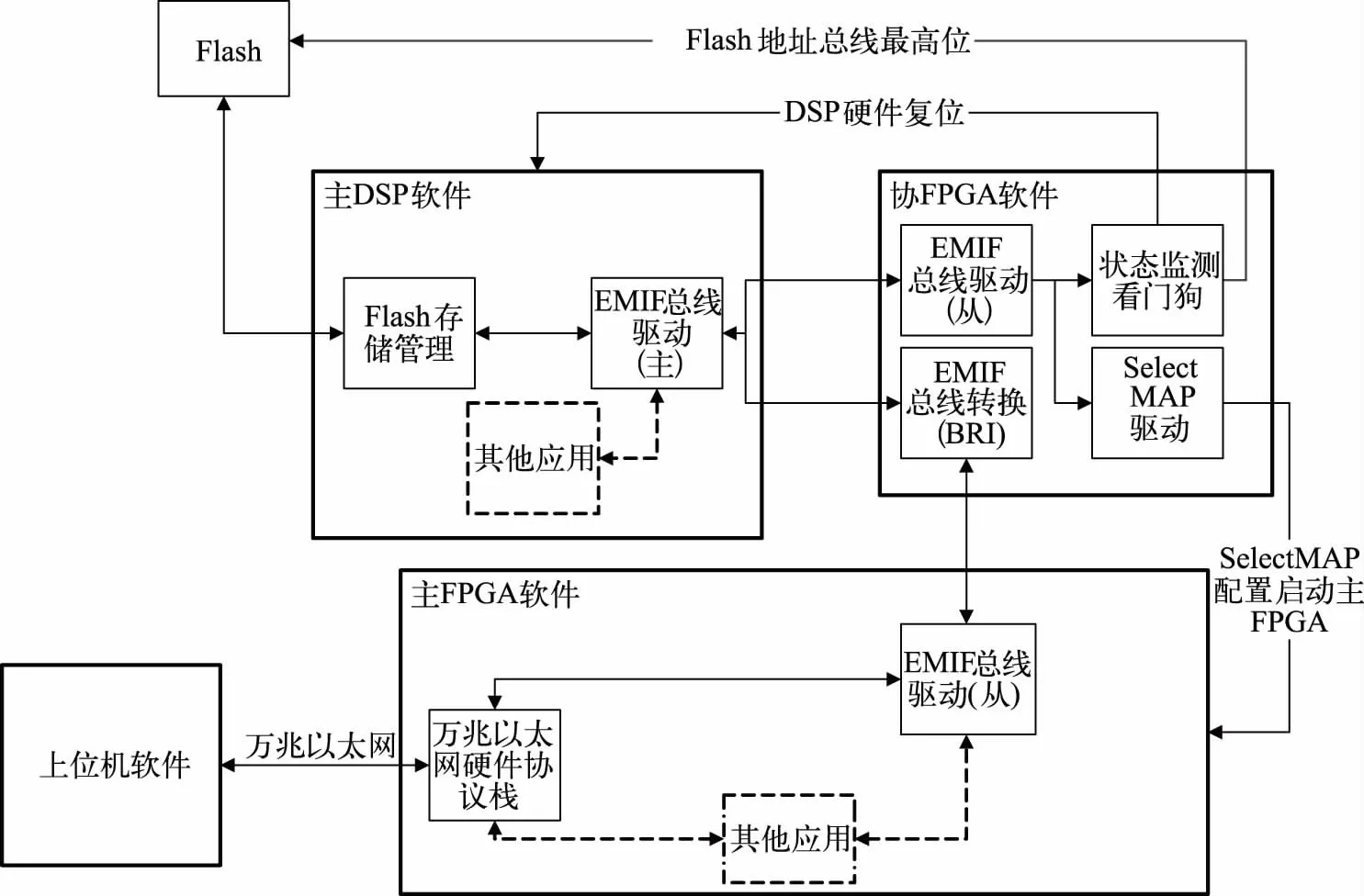

软件系统框图如图3所示,主要由上位机软件、主FPGA软件、协FPGA软件与主DSP软件构成,框图中与固件升级系统无关的软件连接关系均用虚线表示。

3.1 SelectMAP

SelectMAP是Xilinx FPGA比特流加载启动的一种方式,有Master SelectMAP和Slave SelectMAP 2种模式,主要区别是时钟信号CCLK由FPGA产生还是由外部供给,本系统中选择使用Slave SelectMAP模式,CCLK信号由外部供给,这是一种方便使用外围处理器配置FPGA比特流文件的方式[7]。外围处理器、复杂可编程逻辑器件(CPLD)等可通过产生对应的时序来完成对FPGA的加载,这是完成本系统功能的重要技术之一,系统软件框图中的SelectMAP驱动就是将EMIF总线的数据转换为SelectMAP配置时序,从而实现DSP配置FPGA比特流的功能。

图3 系统软件框图

3.2 万兆以太网硬件协议栈

万兆以太网硬件协议栈的技术可参阅文献[8]。本系统中采用的硬件协议栈功能更为完善,在支持地址解析(ARP)、用户数据报(UDP)协议的基础之上,新增支持组管理协议(IGMPv2协议),使协议栈不仅支持单播组网,同时也支持组播组网。在万兆以太网硬件协议栈的加持下,子系统具备了强大的组网能力。

3.3 固件升级流程

系统的应用功能是由主DSP和主FPGA的固件来实现的,所以固件升级的是主DSP和主FPGA的固件,协FPGA固件在第一次固化后就不再升级。固件升级流程如图4所示,上位机通过万兆以太网将升级固件发送给子系统,子系统中的工作流程如下:万兆以太网硬件协议栈将数据解析后发送至EMIF总线,主DSP通过EMIF总线识别读取,升级固件后烧写到Flash中[9]。所有升级数据帧除了以太网协议中的校验外,用户数据中也包含了校验,校验通过后才能烧写到Flash中,校验不通过,子系统会将错误状态上报给上位机。Flash烧写完毕后,DSP还会将固化的固件进行回读比较,以确认烧写的正确性,大大提高了固件升级的稳健性。

由于应用环境的多样性,在一个大系统中所有子系统的应用软件可能是相同的,例如相控阵雷达中各个子阵;也有可能不同的子系统应用软件分为几种类型,需要升级不同的固件。分3种情况说明升级系统的灵活性。

图4 固件升级流程

第1种,所有子系统的固件相同,将所有子系统设置成同一个组播IP(即一个组),上位机向组播IP发送升级数据即可。

第2种,子系统的固件分为几种类型,按类型分类设置不同的组播IP,上位机向不同的组播IP发送升级数据,完成不同类型的子系统固件升级。

第3种,单个子系统的固件升级,上位机向指定的单播IP地址发送升级数据,完成一个子系统的固件升级。

升级系统的灵活性可以满足不同系统的固件升级需求。

以上描述的升级固件包含主DSP软件和主FPGA软件,协FPGA的软件主要为系统的状态监控、异常处理以及接口转换等功能,在调试稳定后不需要进行升级,所以协FPGA的程序单独固化在启动PROM中。

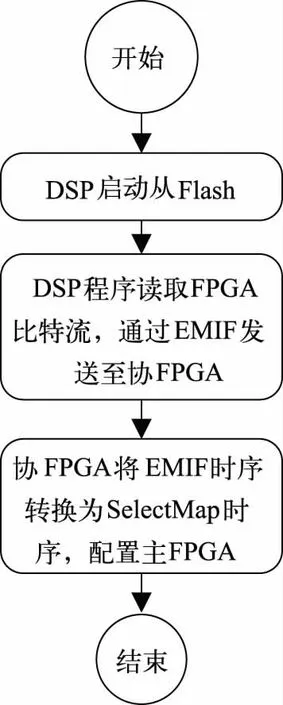

3.4 固件的启动流程

固件启动流程如图5所示,子系统中的工作流程如下:上电后主DSP会自动从Flash中加载程序,DSP启动完成后首先从Flash中读取主FPGA的比特流,并通过EMIF总线发送给协FPGA,协FPGA将比特流转换为SelectMap的时序,完成对主FPGA的配置与启动。

图5 固件启动流程

4 系统稳健性设计

4.1 固件存储的冗余备份

主DSP固件和主FPGA固件是存储在Flash中的,如何避免异常情况导致固件错误是必须要研究的课题。硬件协议栈中的层层校验和回读确认已经能保证固件数据的正确性,还有一种异常情况则是在烧写Flash的过程中系统断电或不可抗力等因素导致固件没有烧写完成,这时Flash中的固件数据不完整,再次上电时主DSP和主FPGA任意一个不能完成启动,子系统将失去再次升级固件的能力,这时需要插入JTAG烧写程序才能再次恢复,这在大的系统联调时是不被允许的,冗余备份则能有效解决该问题。

Flash固件存储结构如图6所示,Flash的存储空间被一分为二,因为Flash的地址总线最高位是由协FPGA控制的(参见图1或3),在子系统挂入大系统之前,黄金固件区和更新固件区均要烧写好相同的固件。当系统级固件升级时,一般只是把固件烧写到更新固件区,这样黄金固件区的固件会始终保持完整,即使更新固件区的固件被损坏,子系统也能利用黄金固件区的固件完成启动。当需要升级黄金固件区的固件时,主DSP需要向协FPGA申请获得Flash最高地址位的控制权,并且升级时需要保证更新固件区固件的完整性。

图6 Flash固件存储结构

4.2 冗余备份的工作机制

主备份的切换启动是由协FPGA来控制的,因为Flash地址总线的最高位和DSP的硬件复位信号均由协FPGA控制(参见图1或3),具体工作原理如下。

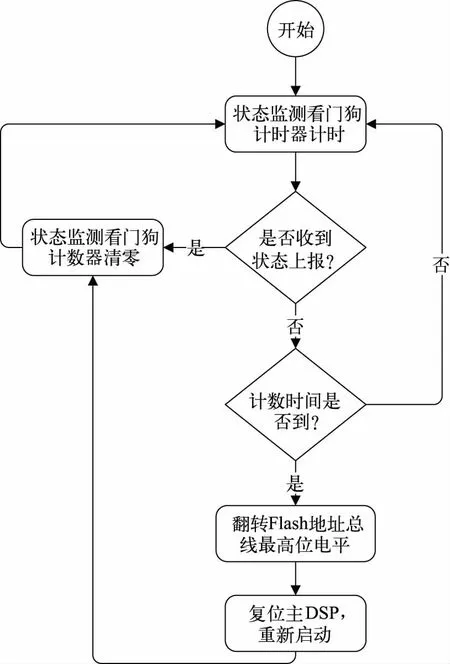

协FPGA内部有一个状态监测看门狗,它是一个定时器,上电以后开始计时。主DSP软件需要间隔固定时间向状态监测看门狗上报状态,当任一固件启动失败时,主DSP不能在规定的间隔时间内向状态监测看门狗上报状态,此时状态监测看门狗将翻转Flash地址总线最高位的电平以切换固件区,并控制主DSP复位,主DSP复位后就可以从新的固件区重新开始启动,其具体流程如图7所示。

5 实施结果

基于FPGA构架的固件升级系统在某型号相控阵雷达上通过了验证,相控阵雷达由一百多个FPGA子系统构成,雷达在系统联调时会对子系统的固件或参数进行反复的升级和配置,使系统完成功能或达到最佳性能。该升级系统可有效支持雷达各子系统固件一键升级,也可只对一个或几个指定的子系统进行固件升级,并且可利用系统灵活的特性对每个子系统进行参数的差异化配置,大大减少了系统的调试工作量,加快了联调进度。

图7 冗余备份切换机制工作流程

6 结论

通过实践验证了基于FPGA构架的固件升级系统设计的正确性。该设计具有快捷、高效、灵活、稳定的特性,同时能兼顾系统应用的高速通信,非常适合大规模使用FPGA构建的系统,可以减少系统联调的工作量,提高效率,具备良好的推广与借鉴价值。