应用于14 bit逐次逼近型ADC的前台数字校准算法*

赵越超,张理振,刘海涛

(1.东南大学微电子学院,南京 210096;2.南京电子技术研究所,南京 210039)

1 引言

随着计算机处理技术的快速发展,模数转换器(ADC)作为模拟、数字信号的桥梁,发挥着越来越重要的作用。不同的应用场景往往对ADC提出高精度、高速和低功耗的要求,并且要求越来越高。在众多的ADC结 构 中,Flash架 构ADC代 表 了 高 速,Delta-Sigma架构ADC代表了高精度,而逐次逼近型(SAR)架构ADC具有面积小、成本低的优点,且能满足大多数场景的速度需求、中高等的精度需求以及较低的功耗需求,所以逐次逼近型ADC是使用最为广泛的ADC架构,在消费类、医疗、工业以及无线通信领域都有它的身影。

随着工艺不断向下延伸,面积不断缩小、器件的失配、系统噪声等的不断恶化使得高精度ADC的设计变得越来越困难。查找目前台湾半导体制造有限公司的工艺手册可以发现,最高的匹配精度是电容值的0.1%,而电容阵列型的SAR ADC只能达到10 bit。所以,要实现精度为14 bit的SAR ADC,需要使用额外的电容误差纠正算法以及噪声消除方法。本文提出了一种在冗余电容结构基础上的数模转换器(DAC)电容失配误差算法,将DAC每位电容引起的电压误差量化出来,通过迭代可求出每位电容的实际权重,并且在数字域上将实际权重加载进去,从而得到实际的输出,以此提高ADC的精度。

2 SAR ADC的原理

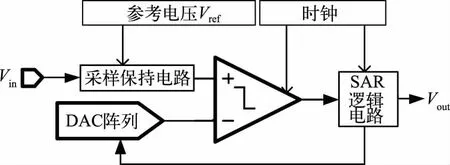

基本的SAR ADC结构如图1所示,它由采样保持电路、DAC阵列、比较器和SAR逻辑电路组成。工作原理基于二进制搜索算法,具体步骤为:输入信号被采样保持电路采样进比较器,SAR逻辑电路将DAC最高有效位(MSB)置为1,剩下低位全部置为0,DAC阵列输出0.5 Vref到比较器的另一端,比较器进行比较,如果输入信号大于0.5 Vref,则输出1,DAC最高位保持不变,否则最高位置为0;接下来将DAC次高位置为1,剩余低位保持不变,如果最高位此时是1,相当于0.75Vref,如果最高位是0,相当于0.25Vref,比较器再与前一位进行比较,结果是1,则次高位保持不变,否则次高位置为0。以此类推,直到最低位(LSB)确定,整个转换完成,整个过程至少需要N个周期。

图1 SAR ADC结构

SAR ADC的常用结构包括电压定标型、电流定标型、电荷定标型以及电阻电容混合结构。电压定标型由于无源电阻匹配精度不高,常用于低精度、低速的ADC中,而电流定标型由于其优越的建立速度,常用于电流舵DAC中,对于中高精度中高速度的ADC,则常采用电荷定标型和电阻电容混合结构。本文考虑到匹配精度、建立速度以及电容式数模转换器(CDAC)电荷定标型没有静态功耗和不需要额外的采样保持电路的优点,选择常用的电荷定标型结构,并使用分段结构降低电容面积,提升建立速度。

3 数字校准算法设计

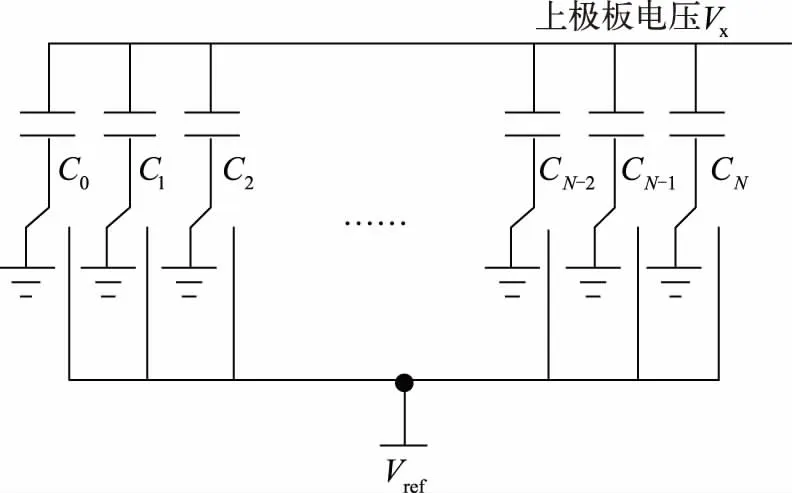

数字校准算法先将DAC阵列中每一位电容所引起的电压误差量化出来,通过迭代可求出每位电容的实际权重,并且在数字域上将实际权重加载进去,从而得到实际的正确输出,图2是二进制加权电容阵列图。

图2 二进制加权电容阵列

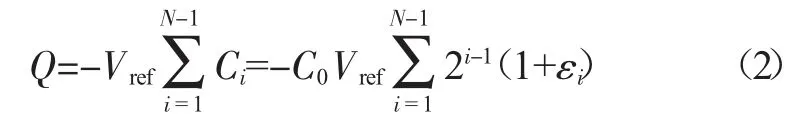

每位电容可表示成

其中,C0为单位电容,其取值决定了工艺所引起的电容失配率,εi是电容失配因子。

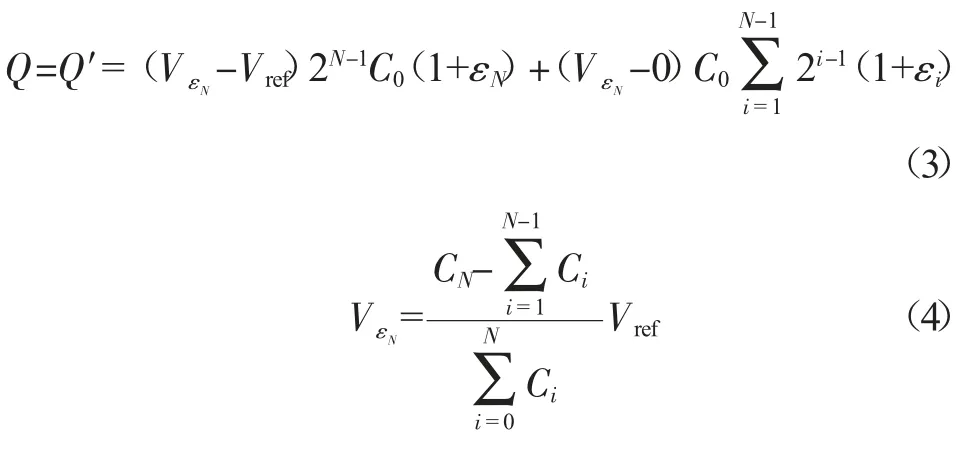

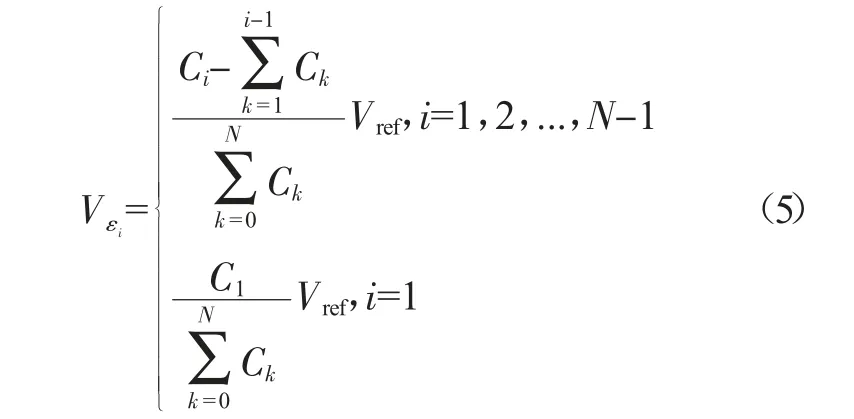

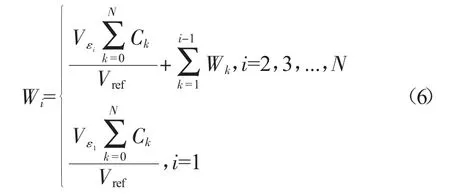

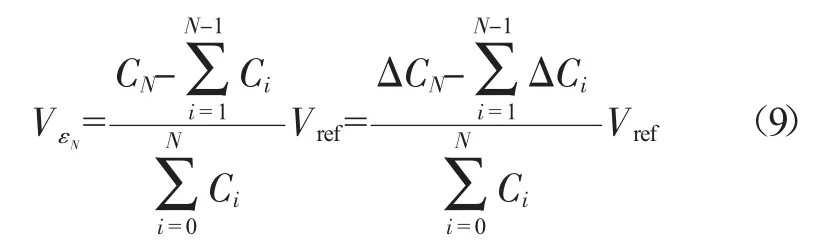

最高位电容CN因失配而引起的误差电压为VεN,剩下的低位电容Ci(0<i<N)因失配而引起的误差电压为Vεi,为了计算每一位电容的失配误差电压,首先计算VεN,将图2中的DAC电容阵列的上极板全部等效接到地,最高位电容CN下极板接地,剩下低位段电容除了LSB C0外的Ci下极板都接Vref,最低位C0依旧接到地,此时电容DAC阵列上所有电容从输出端看,等效的电荷Q可表示为

然后将电容阵列上极板和地断开,并将最高位电容CN下极板接到参考电压Vref,剩下低位段电容下极板等效接到地。假设此时通过电荷转移上极板等效电压为VεN,则根据电荷守恒得

根据上述方法可依次求得其他每位电容引入的误差电压,总结如式(5)所示:

通过式(4)(5)可求得每位电容的实际权重Wi:

至此实际电容权重计算完成,再将权重存入寄存器中,在ADC实际输出量化码后,在数字域上将其加载进去,得到正确的输出。

4 14 bit SAR ADC的数字校准算法设计

4.1 14 bit SAR ADC数字校准算法

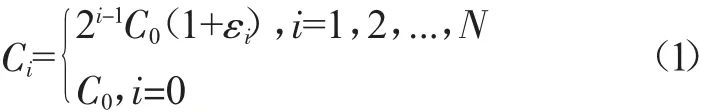

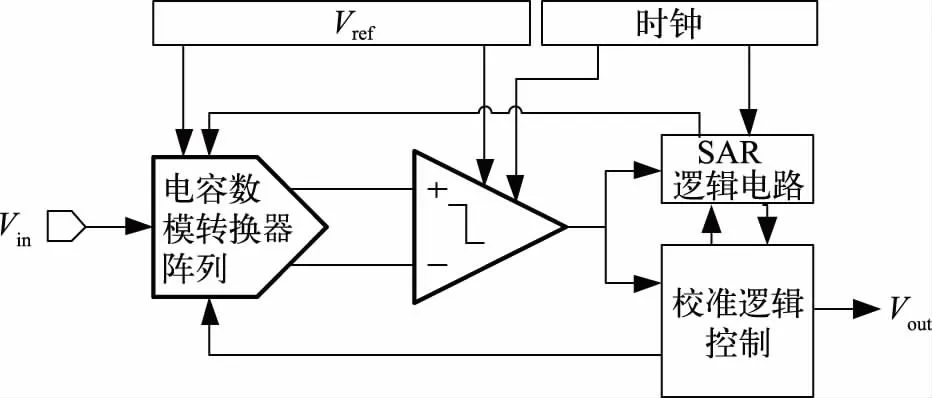

图3是所提出的带有数字校准算法的SAR ADC结构图,它和一般SAR ADC的不同之处在于多了校准逻辑控制部分,且采用分段结构,由8 bit MSB段和6 bit LSB段组成,在高位和低位段插入了冗余电容来纠正因为建立不充分而带来的误判,整个SAR ADC

采用全差分的结构来提升信噪比。

图3 带数字校准算法的SAR ADC结构

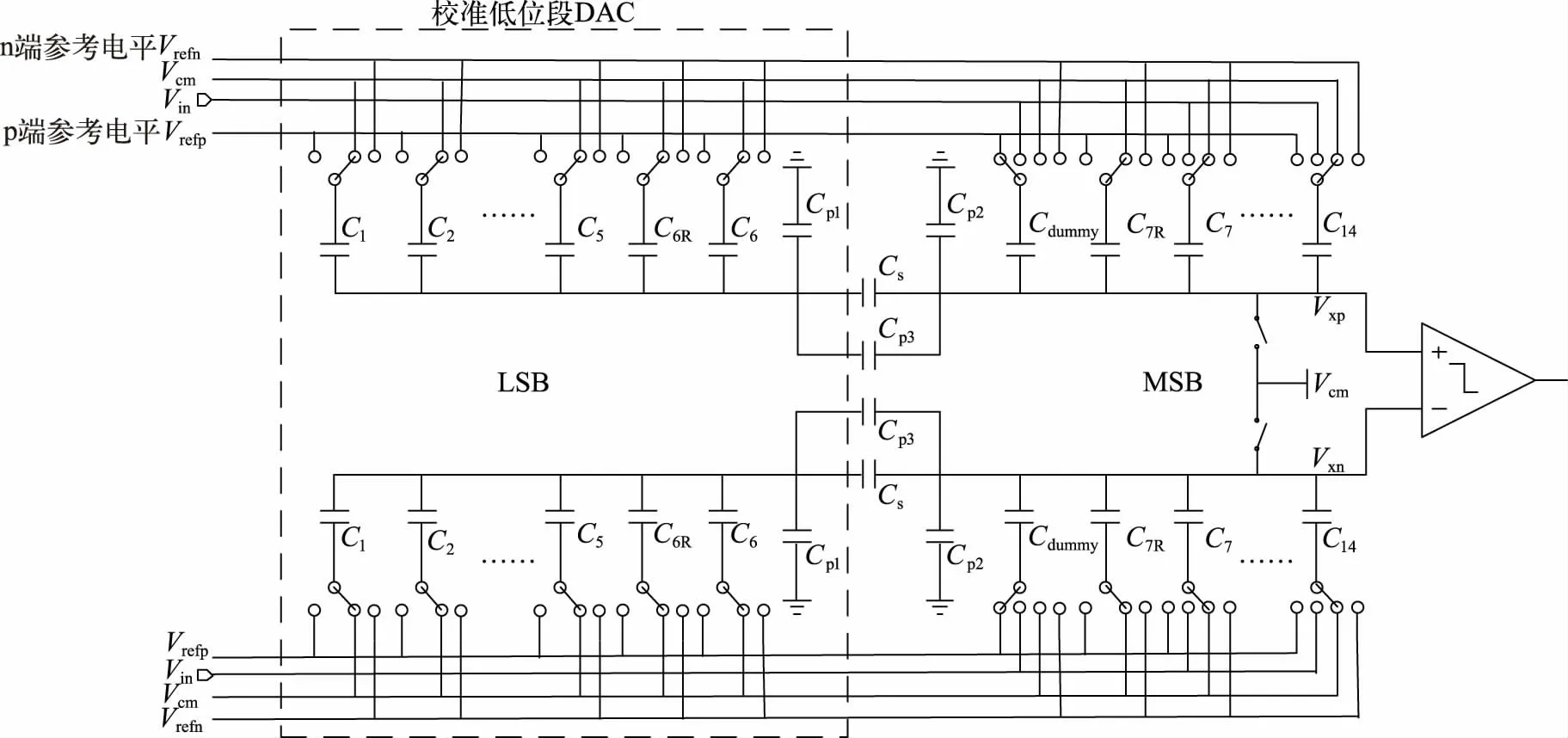

图4为采用的电容阵列DAC结构图,其采用了分段桥接的结构,高位段8 bit和低位段6 bit采用了差分的结构。传统单端结构往往需要1正1负2个冗余电容,差分结构只需要插入1个冗余电容即可实现冗余功能,并且在校准DAC低位段做了细化处理。图4中,Cdummy为补齐电容,Cpx为寄生电容。桥接电容Cs如果采用文献[1]所示结构,则Cs是一个分数电容,为

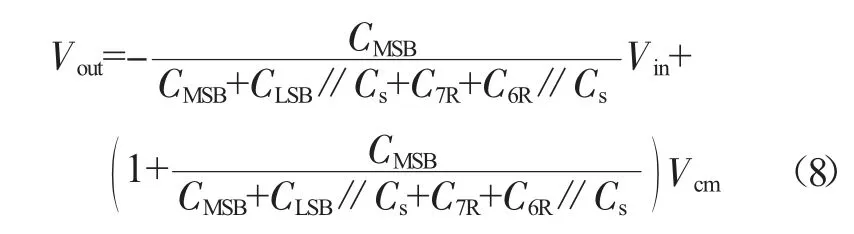

若采用这种结构,14 bit ADC的桥接电容Cs为(64/63)C0,由于实际工艺分数电容不好做,故采用在MSB段补一个单位电容的方式,这样桥接电容为一个单位电容,但由于这种结构存在天然的增益误差,故采用将桥接电容进一步做大的方式,并且插入冗余电容来消除增益误差,且增大了误差校准范围。这时实际的DAC输出为

其中,CMSB为MSB段中除了补偿电容C0和冗余电容C7R外的所有电容,CLSB为LSB段中除了冗余电容C6R外的所有电容,Vcm为共模电平。

整个系统工作可分为校准阶段和正常比较阶段,校准阶段大致原理如下。

由于MSB段电容失配影响远大于LSB段电容失配的影响,故只校准高位段的电容失配以及低位段与高位段的比值系数,首先校准低位段与高位段的比值系数,先校p端。采样阶段:顶板接Vcm,C7R底极板接Vcm,其余也全接Vcm。保持阶段:顶板与Vcm断开,Cp7R(p端C7R)接到Vrefp,Cn7R接到Vrefn,此时采样完毕,通过低位段C0~C6和C6R量化出误差电压,存入寄存器,然后继续校这一位的n端。采样阶段:顶板接Vcm,C7R底极板接Vcm,其余也全接Vcm。保持阶段:顶板与Vcm断开,Cp7R接到Vrefn,Cn7R接到Vrefp,此时采样完毕,通过低位段C0~C6和C6R量化出误差电压,存入寄存器。以此类推,再从高位C14开始校到C7,校准结束。

正常比较阶段大致原理如下。采样阶段:预充电,MSB段除了冗余位Cp7R和Cn7R外的电容底极板采样输入信号,顶板接Vcm,低位段所有电容接Vcm。保持阶段:电荷转移,顶板与Vcm断开,所有电容底极板接Vcm,然后比较,通过整个DAC阵列量化出14位数字码,再将校准阶段得到的高位权重在数字域上乘上14位码累加,最终得到正确的输出。

图4 电容阵列DAC结构

4.2 冗余校准技术

插入低位段冗余位后,校准范围变成

根据文献[3]的思路,设计了适用于全差分分段结构的冗余校准电路,图4中虚线框部分为校准低位段DAC,在低位段插入冗余电容Cp6R和Cn6R,由于冗余电容插入的位不一样,能够容许校准的范围也不一样。

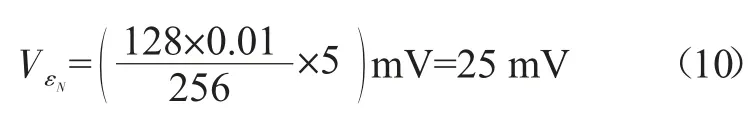

由于电容失配的存在,最大失配误差发生在最高位上,查找工艺文件后,假设最高位电容失配σ达到了1%,则最高位电容引入的误差电压为

所以最坏失配情况下的误差电压为

5 仿真结果

为了展示基于14 bit SAR ADC的前台数字校准算法的效果,搭建了和实际电路高度一致的Matlab模型来模拟SAR ADC的实际工作过程以及数字校准算法的工作过程和效果,并且引入了按照高斯正态分布随机失配的电容阵列以及比较器的失调。

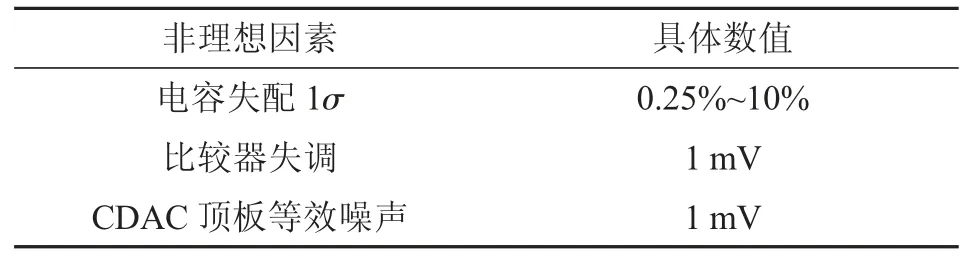

表1 Matlab模型里面引入的非理想因素

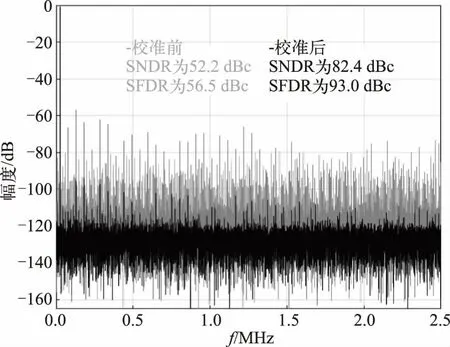

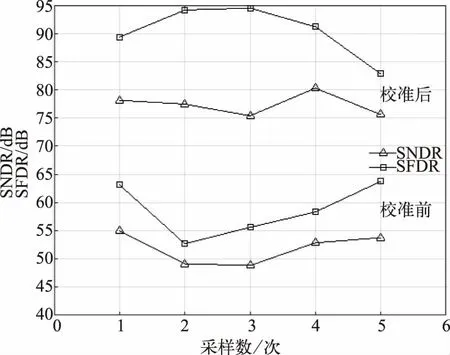

图5、6展示了校准前后的动态性能参数。由图5可知信噪失真比(SNDR)提升了30.2 dB,达到了82.4 dB,无杂散动态范围(SFDR)提升了36.5 dB,达到了93.0 dB。从图6可知,经过多次采样,校准之后比校准之前的性能提升明显,校准算法稳定性较好。

图5 校准前后频谱

图6 校准前后多次采样后SNDR和SFDR性能

6 结论

本论文提出了一种应用于14 bit SAR ADC的前台数字校准算法,搭建了和实际电路高度一致的Matlab模型进行验证,引入了和实际情况一致的非理想因素,并且模拟了比实际情况更加恶劣的电容失配误差,比较校准前后的动态性能,并通过连续多次的采样进行校准前后性能比较,结果显示性能改善情况明显。