抑制CMOS输出端口反向漏电设计

叶宗祥,史良俊

(1.中国电子科技集团公司第五十五研究所,南京210096;2.无锡力芯微电子股份有限公司,江苏无锡 214028)

1 引言

随着半导体集成电路技术的发展,CMOS工艺由于其静态功耗低、速度快、单管面积小等优点被广泛应用于数字电路当中,并且随着特征尺寸的减小及电源电压的下降,其优势越来越明显[1-2]。CMOS输出结构在数字电路中同样占据主导地位[3]。然而,CMOS输出结构在功耗上受漏电的影响较大,对运用了CMOS输出结构的消费电子产品来说,漏电问题对其电池寿命和耐用性有着直接的影响[4]。1997年,SHIGEMATSU等[5]设计了一种多阈值电压CMOS电路(MTCMOS),通过使用断电技术来降低阈值电压和待机漏电。2000年,POWELL等[6]将一种称为“gated-Vdd”的电路机制运用在基层直接渲染(DRI)缓存中,其关键思路为在SRAM单元中的电源或地路径上引入额外的晶体管,晶体管在被使用的部分开启,在未被使用的部分关断,从而关断了缓存中未使用部分的电源电压,并消除了漏电。2003年,MUKHOPADHYAY等[7]提出了一种基于栅极和亚阈值漏电对总漏电的占比输入向量选择技术来降低电路中的总漏电,与传统的晶体管堆叠技术相比,该技术在50 nm器件中降低了44%的漏电。

在便携式设备中,经常存在多种电源供电并存的现象,由于电源启动有先后,会出现后级的设备先供电、前级设备后供电的情况,此时就容易触发后级设备向前级的输出端口漏电的状况。本文针对CMOS输出结构的反向漏电问题,从电路的相关理论出发,基于华润微电子0.25 μm 5 V工艺,设计了一种改良的CMOS输出结构,经过多次迭代仿真、调试及流片,证明其漏电水平符合预期。

2 电路设计及分析

2.1 传统结构

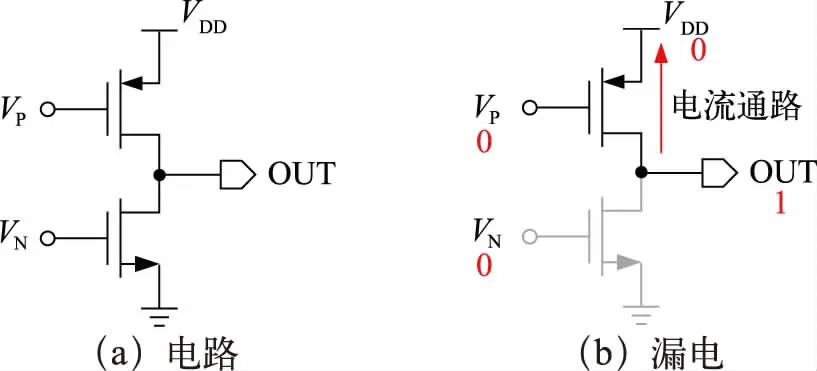

传统的CMOS输出结构如图1(a)所示,该结构由1个PMOS管和1个NMOS管上下堆叠构成,2个晶体管的连接处OUT为输出端口。当该结构运用于数字电路中时,在工作状态下,电压VP和VN由同一个信号控制,在同一时刻只有一个MOS管导通,另一个MOS管截止,在电源和地之间没有直流通路,因此静态功耗几乎为0;在睡眠状态下,PMOS管和NMOS管都关闭,输出表现为高阻,所以静态功耗也为0[8]。该结构利用PMOS管和NMOS管的互补关系,使其具有开/关状态强、噪声容限大、扇出能力强、可控性好、输入阻抗高以及静态功耗低等优点,因此受到人们的青睐而应用广泛[9-10]。但是传统结构在某些特殊应用场合下存在缺陷,图1(b)为其漏电示意图,当输出端口被上拉而先于电源上电时,输出变为高电平,而输入端口处无信号输入,PMOS管栅极所接的VP和电源都变为低电平,进而导致PMOS管导通。在这种情况下输出与电源之间存在着一条导电通路,而导通的PMOS管阻抗较小,从而在该通路上产生大电流,导致不必要功耗的增加,甚至有烧坏电路的风险。

图1 传统的CMOS输出结构电路和漏电示意图

2.2 改良型结构

2.2.1 改良型结构整体电路

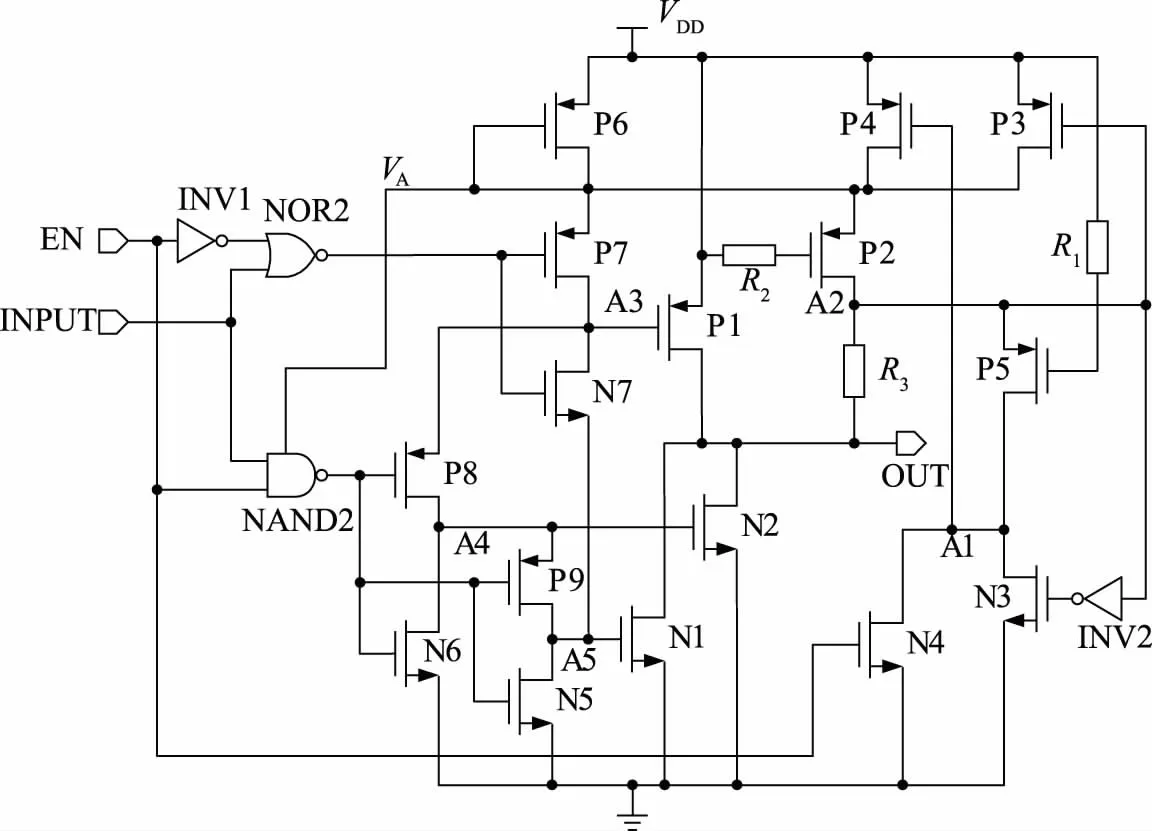

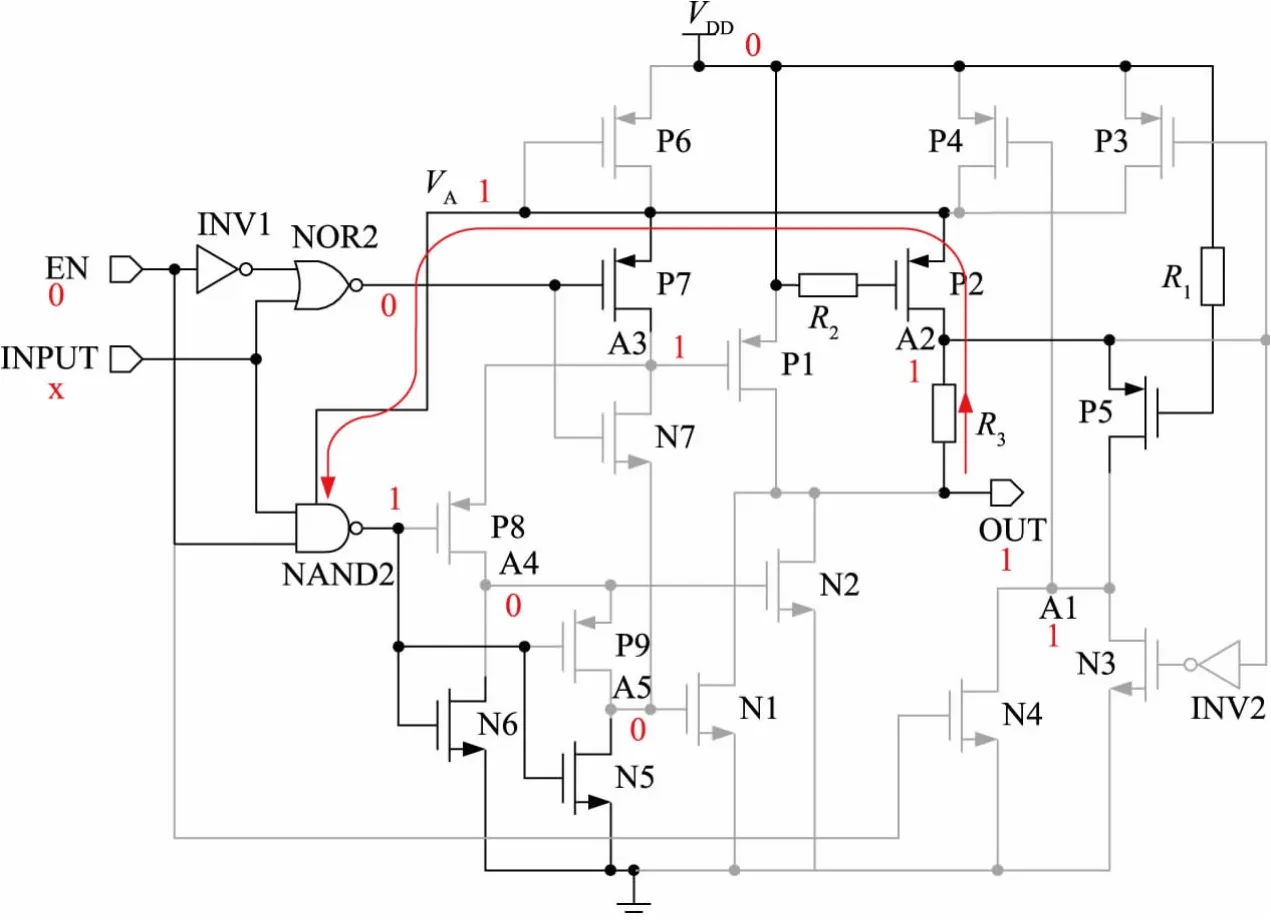

为了解决传统CMOS输出结构反向漏电问题,本文提出的改良型CMOS输出结构电路如图2所示,其特点为通过引入额外的使能信号和供电的中间节点,在特定情况下,以内部逻辑控制电路抬高中间节点电压,避免出现大电流导通路径,从而解决漏电的问题。在图2中,EN为使能信号,INPUT为逻辑输入信号,P1、N1和N2为输出驱动管。需要注意的是,图中与非门NAND2的供电电压为VA;PMOS管的阱电位(衬底电位)有2种接法,一种是接到电源VDD,另一种是接到中间节点VA。

图2 改良型CMOS输出结构电路

2.2.2抑制反向漏电原理分析

当电源正常供电时,P6以二极管连接器件的形式导通,为节点VA提供接近于电源VDD的电压。此时,可根据使能信号EN的状态,对电路的功能进行分析。

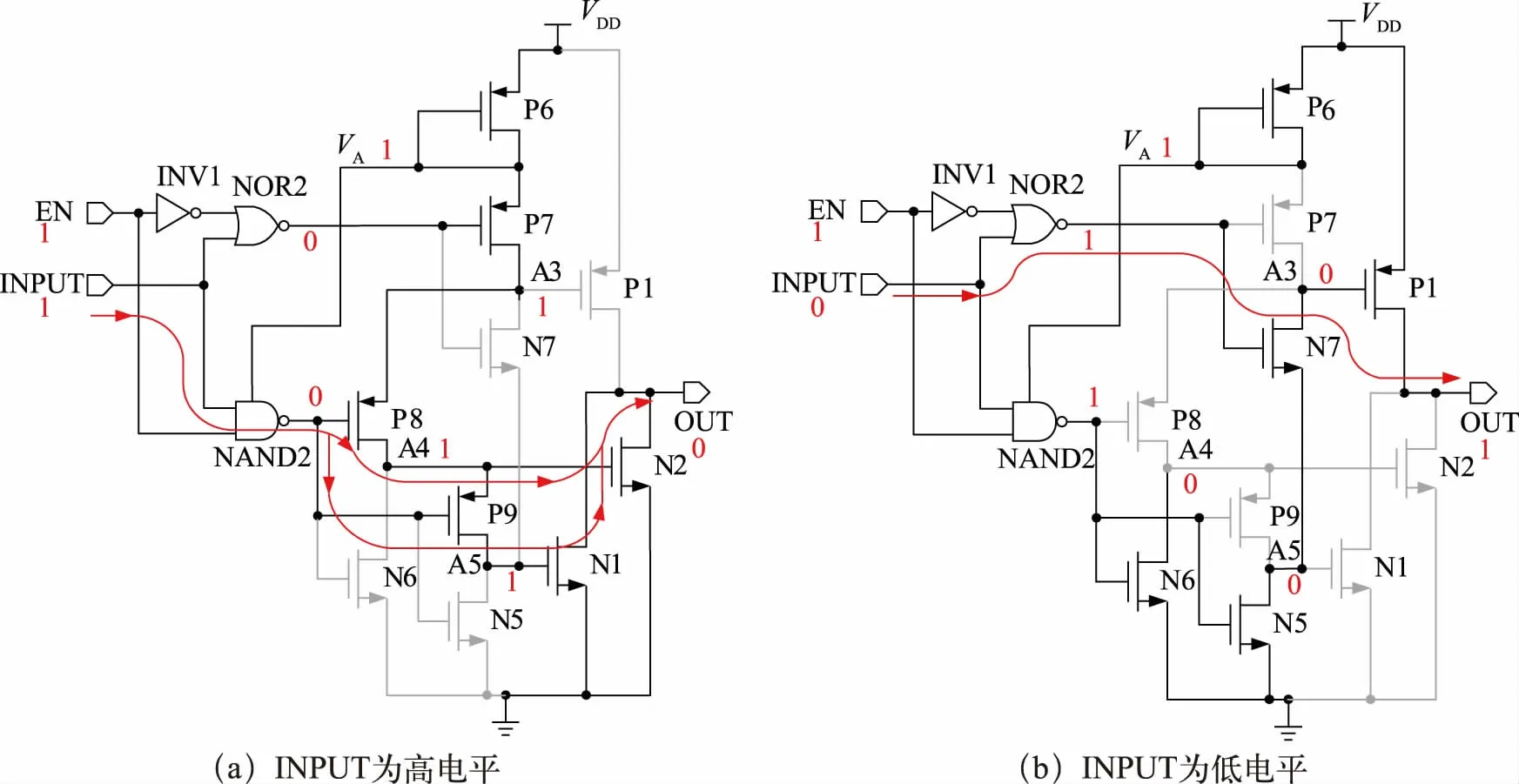

当EN为高电平时,N4导通,节点A1的电压被下拉,进而P4导通,VA进一步被上拉,并基本和VDD保持相同。此时,或非门NOR2和NAND2都对INPUT实现了取反的功能,并通过进一步推理,可得该电路INPUT与OUT的逻辑关系为OUT=INPUT,其中INPUT分别为高电平和低电平时所对应的信号路径如图3(a)、(b)所示(为简化分析,已略去部分电路,灰色表示处于截止状态)。

当INPUT为高电平时,NOR2和NAND2的输出为低电平,P7、P8和P9相继导通,进而节点A4和A5都变为高电平,分别驱动N2和N1,使OUT变为低电平。此时的主信号路径由NAND2、P8和N2(P9和N3)组成。

当INPUT为低电平时,NOR2和NAND2的输出为高电平,N5导通,节点A5变为低电平,给N7创造了导通的条件,N7导通,节点A3也变为低电平,驱动P1,使OUT变为高电平。此时的主信号路径由NOR2、N7和P1组成。

图3 EN为高电平时电路的逻辑取反功能

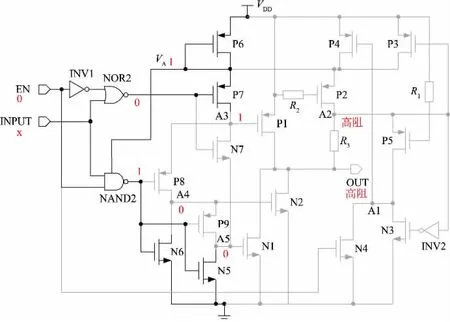

当EN为低电平时,输出高阻态如图4所示,NOR2的输出为低电平,P7导通,N7截止,节点A3变为高电平,使得P1截止;NAND2的输出为高电平,N5和N6导通,节点A4和A5变为低电平,使得N1和N2截止。由于输出驱动管P1、N1和N2都截止,OUT表现为高阻状态,此时,P2、P5和N4也都截止,其所在支路上也无电流通路。

在EN为低电平时存在一个隐患,节点A2通过电阻R3与OUT连接,稳态下A2的电压与OUT相同,而节点A2又作为若干器件及反相器INV2的输入,当反相器的输入为高阻时,一定会导致在反相器中存在大量的泄漏电流。因此在实际使用过程中,要求OUT在高阻状态下通过电阻R3连接至高电平电位,从而避免在输出高阻态时引起漏电问题。

输出高电平、电源低电平时抑制漏电原理如图5所示。当VDD没有被供电(为低电平),而OUT接高电平,INPUT和EN也均为低电平时,由VDD供电的逻辑门INV1、INV2和NOR2的输出也为低电平。节点A2为高电平,P2和P5的栅级分别通过电阻R2和R1连接到VDD,所以P2和P5导通。节点A2的电压可通过P2传递给节点VA,进而为电路提供供电电压,使得P7导通。NAND2由VA供电,在其2个输入都为低电平的情况下,输出为高电平,使得N5和N6导通。除P2、P5、P7、N5和N6导通之外,其余晶体管均处于截止状态,在节点VA到电源或地之间均不存在电流通路。

由上述分析中可以看出,在正常供电时,电路可以实现正常的逻辑输出功能;而在电源未上电或接地、输出端口接高电平时,可以通过内部的控制电路将输出端口的高电平传递给电路进行供电,并使得电路中绝大部分晶体管处于截止状态,避免出现导通的支路,从而抑制输出端口对电源的漏电。但是该改良型结构也存在一定的缺陷:首先,结构较复杂,相较传统CMOS输出结构的二管单元,以牺牲成本的代价实现了特殊条件下的应用功能;其次,在正常工作时,高阻态输出不能悬空,需要接到相对较高的电平,否则内部的反相器会产生漏电通路。

图4 EN为低电平时输出的高阻态

图5 输出高电平、电源低电平时抑制漏电原理

3 电路仿真与测试

采用华润微电子0.25 μm 5 V工艺搭建电路结构,漏电分析直流仿真电路如图6所示,图中AD0~AD3、BD0~BD3为2组输入端口,AO0~AO3、BO0~BO3为2组输出端口,具有一一对应关系,采用本文提出的方案设计每一个输入至输出的结构,AOE和BOE为使能端口。在进行直流漏电情况仿真时,将其中4个输出端口AO0、AO1、AO2和AO3都短接到高电位(3 V),其他所有端口及电源端保持悬空。仿真结果表明,4个输出端口处的总漏电流只有0.4 nA左右。

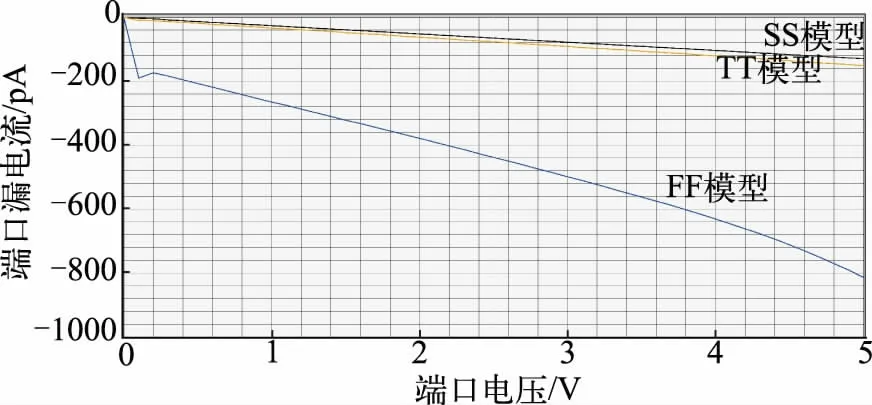

3种不同模型(TT、FF、SS)的单端口漏电仿真波形如图7所示,仿真条件:温度为27℃,端口电压为0~5 V,除了仿真的输出端口外,其他的输入/输出都悬空。可以看到,SS模型和TT模型漏电在200 pA以内,FF模型漏电较大一些,但最高也不到1 nA。

图6 漏电分析直流仿真电路

图7 不同模型下的漏电仿真波形

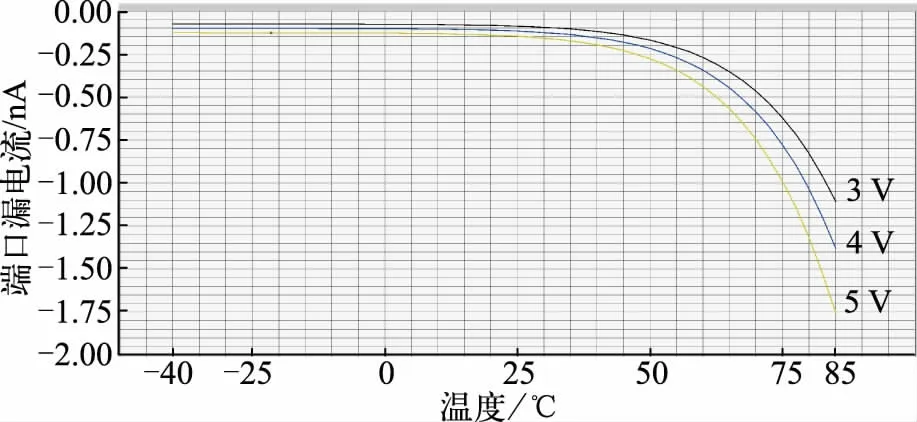

不同温度下的端口漏电仿真波形如图8所示。仿真条件:模型为TT,端口电压分别为3 V、4 V和5 V,温度扫描范围为-40~85℃。随着温度的升高,漏电流明显增加,其中漏电流从大到小对应的端口电压分别为5 V、4 V、3 V。即便在5 V端口电压下,在85℃时最大漏电流也只有1.75 nA。

图8 不同温度下的漏电仿真波形

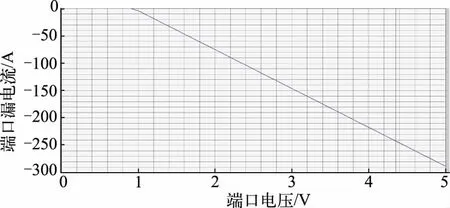

采用同样宽长比(PMOS管的宽长比为630 μm/0.5 μm,NMOS管的宽长比为364 μm/0.55 μm)时,常用结构的CMOS输出端口漏电情况仿真结果如图9所示,宽长比和本文论述的实例相同。仿真条件:模型分别为TT、FF和SS,温度为27℃,扫描电压范围为0~5 V。可以看出,在理想情况下,5 V时的漏电流已经超过了250 A,因此对于常用的CMOS输出结构,在使用时,禁止出现电源不上电而将输出端口置成高电平的情形。

图9 常用的CMOS输出端口漏电仿真波形

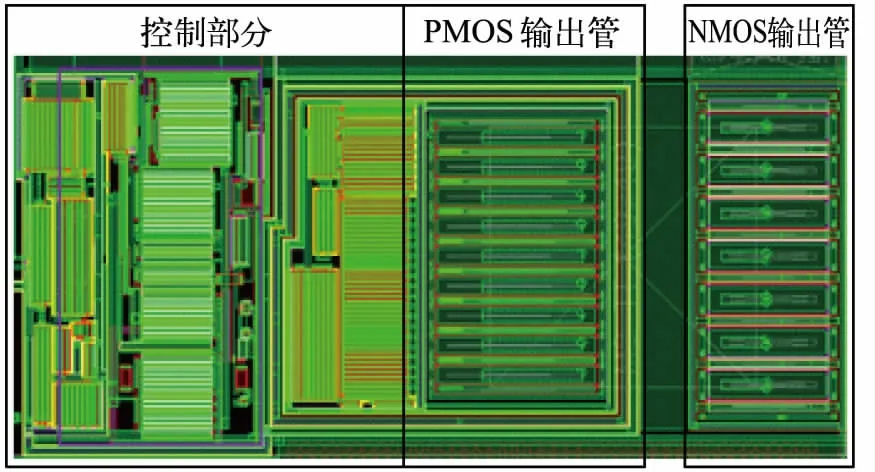

在仿真结果符合预期后,对其进行版图设计并流片,采用华润微电子0.25 μm 5 V工艺,版图如图10所示(为便于观察,已将上层铝线隐去)。在版图中左侧为控制部分,右侧为按照静电放电(ESD)规则设计的驱动管。

图10 本设计完整版图

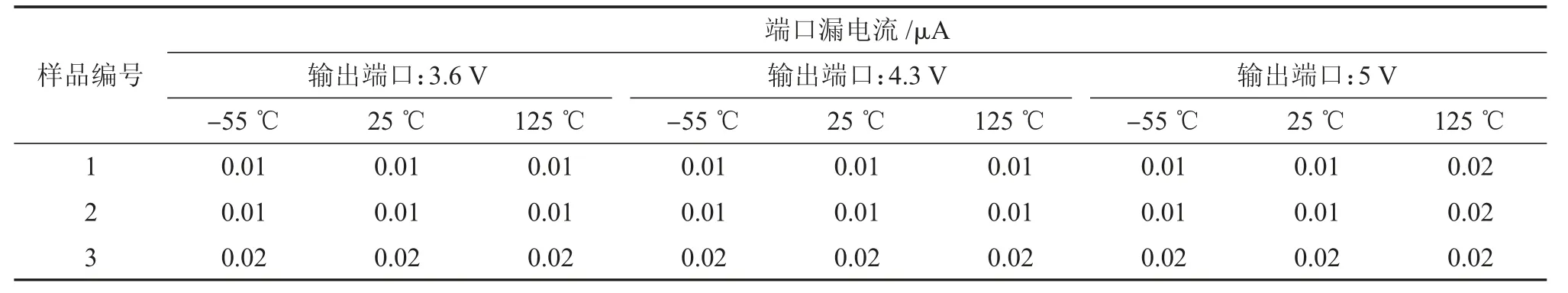

输入端口悬空,输出端口分别加3.6 V、4.3 V以及5 V电压,在-55℃、25℃和125℃温度下对样品进行测试,测试结果如表1所示。测试规范为电流小于10 μA,实际测试时,在-55~125℃范围内,端口漏电流均接近0 A(万用表测试最小精度为0.01 μA)。

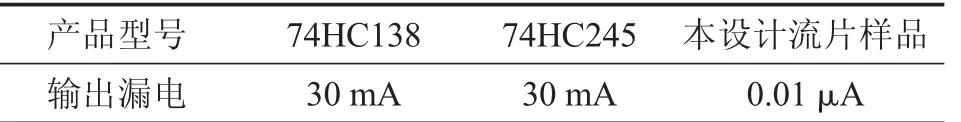

将本文提出的结构与传统结构的电路端口漏电进行对比测试,结果如表2所示。测试在常温下进行,芯片的输入端口以及电源端口悬空,输出端口外接电源电压3 V,限流30 mA。根据测试对比可见,传统的CMOS输出结构在电源不上电而输出端接高电平时漏电非常大,电流直接为外接电源的限流值,采用本设计方案流片的样品漏电则非常小。

表1 实际样品端口漏电测试结果

表2 端口漏电对比

4 结论

本文提出了一种能够抑制CMOS输出端口反向漏电的结构设计,传统CMOS输出结构在电源断电或者悬空而输出端口接高电平时会存在较大的反向漏电,本文通过优化结构,在该特定状态下以输出端口为内部电路供电,并通过逻辑组合,使得输出端口到电源或者地之间没有导电通路,从而抑制了反向漏电的情况。该结构性能可靠,适用于一些特殊应用场合。