S波段10 W LDMOS功率管匹配电路设计

王 涛,潘建华,徐 政

(无锡中微晶园电子有限公司,江苏 无锡 214035)

1 引言

RF LDMOS功率管具有高输出功率、高增益、高线性、良好的热稳定性等优点,广泛应用于移动通信基站、数字广播电视发射以及射频通信领域[1]。其在国防科技和军事通讯领域的作用显得更加突出,在相控阵雷达、机载舰载雷达领域作为发射通道的功率放大器,缩小了装备的体积,减轻了重量,并且具有更高的可靠性及更长的使用寿命。

阻抗匹配是LDMOS功率管应用电路设计的关键任务,射频模块的主要任务是在无相移的情况下确保最大功率传输[2]。阻抗匹配是通过阻抗匹配网络将初始的阻抗转换至标准参考阻抗50 Ω或其他需要的阻抗。在实际的射频电路设计中,大多数模块的输入输出阻抗被匹配至50 Ω,其原因是几乎所有的射频测试模块测试仪器均采用50 Ω作为标准参考阻抗。

S波段LDMOS功率管经常应用在宽带情况下,因此对LDMOS功率管外匹配电路设计的研究尤为重要。在窄带和宽带情况下的阻抗匹配方法基本相同。窄带情况下,其中心频率可以近似代表整个带宽,所以阻抗匹配过程中只需要考虑一个频点。宽带情况下,初始阻抗在史密斯圆图上是一段阻抗曲线而不是一个点。阻抗曲线上的每一个点代表带宽内每个频率所对应的阻抗值。宽带匹配的主要分析放在从窄带到宽带的频率扩展方法上。为了将终端阻抗匹配从窄带变为宽带响应,要压缩回波损耗轨迹并把它移到史密斯圆图的中心[3]。

2 匹配电路设计方案

2.1 偏置电路设计

偏置网络是线路设计关键的一环,其主要有以下功能:(1)保持电路稳定性,消除自激振荡;(2)阻止射频能量进入源极、漏极偏置电压供应线路;(3)阻止电源噪音到达场效应管的源极和漏极;(4)在漏极提供高阻抗,使其对射频主电路微波特性影响尽可能小,即不引入大的附加损耗、反射以及高频能量沿偏压电路的漏泄等,以保证在工作频段内得到最佳射频性能[4]。图1为LDMOS偏置网络示意图。

图1 LDMOS偏置网络

λ/4微带线依靠旁路电容C8到C12取得接地的低阻抗通道。λ/4微带线的电抗要至少大于管子的漏极阻抗的10倍,还需要考虑能够承受漏极直流电流;L2尽可能大,以便在带宽内形成足够高的阻抗,也需要能够承受漏极直流电流,并且直流电阻要足够小,从而消耗在电感两端的直流电压最小。λ/4微带线和C8联合使用大大降低出现在漏极偏置电压供应线路的载频能量。λ/4微带线在这个频带内起阻碍作用,C8用来进一步压制工作频带内的射频能量,把能量旁路至地。C8容值应选成使其串联谐振频率FSR接近放大器工作频率,在串联谐振频率时呈现低阻抗,射频能量由它旁路到地。

C9~C12主要用于直流电源的去耦,电容C9~C12的容值逐个下降,挑选时使它们在首尾相连的几个频段中的阻抗和感抗都低,因此它们对低于放大器工作频带的功率提供连续的旁路。在电容之间也可以使用铁氧体磁珠,磁珠固有的Q值很低,因此可以在很宽频带上排除电源噪音,而且把各个电容元件分隔开来。

2.2 阻抗匹配网络设计

对于大功率LDMOS功率管,输出匹配网络用来实现功率管的输入端口与信号源的共轭匹配,减小输入信号的反射;输出匹配用来完成功率管的输出端口与负载之间的最大功率匹配。

采用负载牵引测试技术得到LDMOS功率管在大信号状态下最大输出功率对应的输入阻抗及输出阻抗。外匹配采用合适的拓扑网络,使LDMOS功率管的输入阻抗与信号源阻抗匹配,输出阻抗与负载阻抗匹配。在S波段,外匹配电路常用串联阻抗阶跃变化的微带线,这种微带结构容易通过仿真软件计算,仿真结果较为精确,而且这种电路结构尺寸小,可以节省电路空间,并可以实现电路的宽带特性。

在3.1~3.4 GHz带宽内,选择靠近中心频率的3.3 GHz频点,串联阶跃阻抗微带线,实现输入阻抗匹配至源端阻抗50 Ω,输出阻抗匹配至负载阻抗50 Ω,其匹配路径如图2所示。

3 电路仿真及调试

3.1 输入匹配电路设计

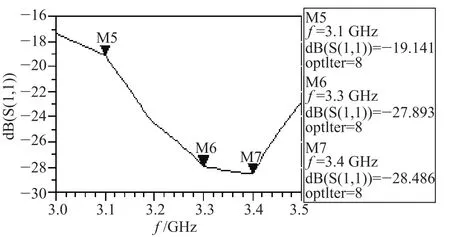

为改善3.1~3.4 GHz带宽内输入端口的驻波,同时考虑偏置电路对匹配电路的影响,建立如图3所示的ADS原理图。该原理图包含偏置电路,理想微带线用实际微带线代替。为了让仿真软件自动优化仿真结果,把需要调谐的微带线长度、宽度设置为变量,并设置调谐范围。利用软件的参数优化控件,设置优化变量为dB(S(1,1)),优化目标为dB(S(1,1))≤-15 dB。

ADS软件仿真优化结果如图4所示。带宽内S11≤-13.5 dB,输入端驻波VSWR≤1.53。

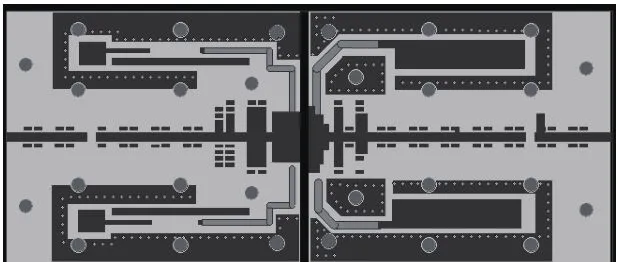

仿真优化的带偏置电路外匹配电路的输入匹配电路版图如图5所示。

图2 匹配路径

图3 输入匹配电路ADS原理图

图4 输入匹配电路仿真优化结果

3.2 输出匹配电路设计

同样,为改善3.1~3.4 GHz带宽内输出端口的驻波,同时考虑偏置电路对匹配电路的影响,建立如图6所示的ADS原理图。由于样管输出阻抗相比于输入阻抗的离散性更小,设置优化目标为dB(S(1,1))≤-20 dB。

图5 输入匹配电路版图

图6 输出匹配电路ADS原理图

图7 输出匹配电路仿真优化结果

仿真优化的带偏置电路外匹配电路的输出匹配电路版图如图8所示。

图8 输出匹配电路版图

3.3 PCB板设计

采用PCB版图设计软件Altium Designer 6.9绘制PCB版图,LDMOS功率管的输入、输出匹配电路版图参数已由ADS仿真得到。外匹配电路采用PCB板材参数为F4B-2,其介电常数为2.55,板材厚度为0.8 mm。根据绘制的PCB板版图加工PCB板,后续在PCB板上安装电容、电阻、电感元件后,完成外匹配电路的制作。图9为LDMOS功率管外匹配电路PCB版图。为方便调试,在微带线旁边画一些调试用的小岛。

图9 LDMOS功率管外匹配电路PCB版图

4 试验结果

图10为完成调试的S波段LDMOS功率管外匹配电路照片。

图10 微波参数测试系统

表1为S波段LDMOS功率管完成外匹配调试后的测试数据,在3.1~3.4 GHz频率范围内,输出功率大于13.8 W,功率增益大于12.4 dB,效率大于37.9%,输入回波损耗小于-8.5 dB。

表1 样管在外匹配电路测试架上测试结果

完成匹配电路调试后,采用负载牵引测试技术测试功率管在外匹配电路上输出端口的驻波。功率管3.1~3.4 GHz带宽内各频点的输出端驻波列于表2。

表2 带宽内各频点的输出端口驻波

从结果看出,功率管在外匹配电路测试夹具上输出端口具有良好的驻波特性,表明功率管外匹配电路调试状态较理想。

5 结论

本文选择中国电子科技集团公司第58研究所研制的S波段10 W LDMOS功率管,以内匹配功率管大信号负载牵引测试提取的输入阻抗、输出阻抗为基础,利用微波仿真工具ADS设计输入、输出匹配电路匹配路径,并用软件的参数优化控件,完成输入匹配、输出匹配电路的仿真,得到输入匹配、输出匹配电路版图。参考外匹配电路设计结果,并根据调试金属片在不同位置时微波参数的变化,经过精心调试,使S波段LDMOS功率管输入回波损耗、增益、增益平坦度、输出功率、效率、谐波等技术指标达到设计要求。最终,采用负载牵引测试手段,验证了功率管的外匹配电路输入、输出端口均有良好的驻波特性。完成匹配电路设计的S波段LDMOS功率管在3.1~3.4 GHz频率范围内,输出功率大于13.8 W,功率增益大于12.4 dB,效率大于37.9%,输入回波损耗小于-8.5 dB。

[1] 黄晓兰,等. 功率RF LDMOS的关键参数研究[J].半导体学报,2006,12.

[2] M M 拉德马内斯. 射频与微波电子学[M]. 北京:科学出版社,2006.

[3] Richard Chi-Hsi Li. 射频电路工程设计[M]. 北京:电子工业出版社,2011.

[4] 耦合,隔直和旁路电容的精度选择[J].MPD微波产品文摘,2001, 09.

- 电子与封装的其它文章

- 毫米波射频互连微组装工艺优化研究*