基于故障预测提高FPGA回写效率

胡中泽

(安徽理工大学,安徽 淮南 232000)

一、简介

随着可编程逻辑器件被广泛应用于当下人们生活的各个领域中,其可以通过硬件修补和升级,使新产品能快速地进入市场领先竞争对手而受到生产商的青睐。这些器件,特别是现场可编程门阵列(FPGA),曾经只在开发阶段才使用的可编程逻辑器件现在被认为是专用集成芯片(ASIC)的很好替代品。FPGA的特点主要包括:易于原型化,减少了设计和测试阶段,缩短了进入市场的时间,特别是在生产过程中可纠正开发缺陷的可能性。

目前最先进的FPGA使用静态RAM(SRAM)存储单元来存储实现的设计,相比于基于闪存的设备,提高了配置存储器存取时间和提供无限数量的配置。基于SRAM的器件最主要缺点是对辐射的敏感性,表现为一个单一的事件的形式翻转,这使得因其低成本、高性能的能力,包括提高他们的可靠性性能的附加层的自定义的现成(COTS)设备成为趋势。因此,一些制造商已经广泛研究COTS设备中的辐射效应,将它们暴露于高辐射剂量,并为系统设计者提供诸如回写和时间/空间冗余等信息和技术,以克服这些影响。在这种情况下,回写指定了一种方法来处理SRAM配置内存中的错误,随着时间的推移,只需刷新它的内容即可,它复制了通常的FPGA启动过程,指定用户设计的位流定期从外部永久存储器加载到内部SRAM配置存储器,系统设计人员可以决定回写的使用,并根据所需的可行性和实施系统的性能,确定回写是瞬间还是周期。

基于真实的FPGA的生产系统受故障影响,表现出高的错误延迟,并且存在交互故障。在后一种情况下,多个错误的组合产生一个系统故障,当单独发生时不会发生,因此,可以通过使用某种形式的回写技术来改善这种系统的可行性。由此提出和探讨从FPGA嵌入式传感器,以及来自外部来源的数据,如何连续调整回写参数。

在这种情况下,基于故障预测,使设备能够满足:一减少回写机制的侵扰,通过激活它只在需要的时候,而不是使用整个周期的方法;二通过激活较少的回写机制,改善功耗;三增加一级系统的可靠性,应对动态环境和硬件老化;此外,这种方法也减轻了系统设计人员对可靠性的考虑及其规范。

二、部分动态重构

最高性能和容量的FPGA在操作过程中使用SRAM单元存储它们的配置。在启动时,该配置内存的内容从永久存储中初始化,该存储保存用户实现的设计(比特流),当放置在恶劣的环境中,甚至在出现一些制造或老化缺陷时,这些设备可能会出现故障,从而在配置内存中产生错误。

为了避免可编程逻辑器件中错误的积累,制造商引入了错误检测和纠正机制(如ECC和循环冗余校验(CRC)),虽然有效,但是提出了一些限制:ECC允许最多,双错误检测和单纠错每帧——在FPGA最小的可寻址单元和CRC是全局配置存储器。由于检测多比特错误帧的难度,制造商在FPGA外部引入回写机制,将可编程逻辑器件中的内容定期重新从永久存储记忆中重载。这种方法有一些缺点:一是固定时间的入侵。由于需要停止所有的模块在FPGA运行,加载原始配置存储器的内容,并重新启动;二是系统状态在应用程序中需要一个专门的分布式的内存文件系统,来减轻内存压力确保模块拥有快速大量的数据读写能力;三是需要外部硬件支持,缓慢的外部接入接口(JTAG,Select Map)等。

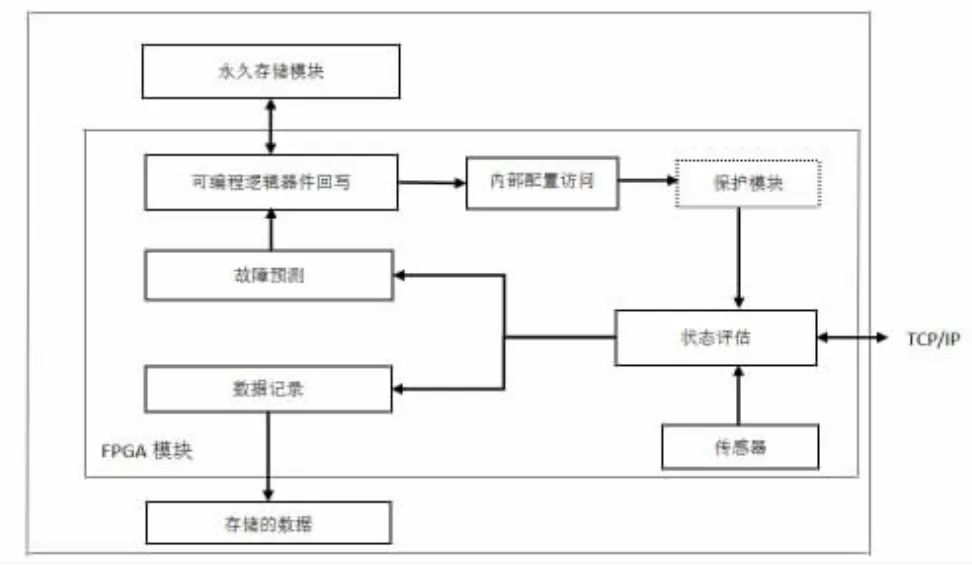

随着部分动态重构(PDR)的引入,支持FPGA资源的时间复用,可以使用小部分设备区域来执行整个时间的不同任务,根据需要重新配置FPGA的专用区域,从而增加间隔尺寸。使用内部配置访问端口(ICAP)接口的可编程逻辑器件,减少了对外部组件的依赖支持回写,因此,在相同的应用程序中使用更小的设备,降低了功耗;为了减少时间的侵扰和避免额外的外部硬件支持回写使用,可以利用PDR,这让我们在使用FPGA的逻辑单元实现回写,同时减少重构延迟;为了在回写器和受保护模块之间提供必要的隔离,后者可以在可重构分区(RP)中实现。此RP在图1中显示,虚线表示FPGA的区域,该区域将被刷新。

该设备同时还包含了几个内部传感器(温度、输入电压等),用于监视设备的正确功能,并通过led的组合通知用户各种错误状态。

图1 故障预测在开发板中实现

三、故障预测回写

敏感的实时系统有非常严格的时序要求,在这样的系统中使用简单的技术回写存在较大的功耗和侵扰,并且系统也缺乏改变操作环境所需的适应性。本文研究的方法是试图使可编程逻辑器件保持相同的能力,以消除潜在的错误,同时满足回写频率,达到操作环境所需的性能和实际设备状态。

1.系统架构

本文提出的系统架构是基于一个额外的组件,命名为故障预测回写,在FPGA可编程逻辑实现(见图1)。此组件负责在需要时触发受保护模块(PM)的部分重新配置。它从FPGA内部和外部收集来自不同来源的信息。这个组件由四个不同的模块组成:

配置记忆洗涤器(CMS);

健康评估(HA);

故障预测(FP);

日志记录器(DL)。

CMS模块的接口与ICAP通过一个PLB总线连接,用于重新配置的目的和外部永久记忆,也是存储PM比特流的地方。它是由FP去重启可编程逻辑器件,也可由故障注入器在评估阶段。

HA模块通过TCP/IP连接从内部FPGA传感器和外部数据源接口收集数据,以收集有关操作环境条件的信息此模块向FP提供相关数据。在特定情况下,PM输入和输出的范围是有界的,并且预先知道,HA组件可以连续监视其接口以检测即将出现的问题。

FP模块实现了基于故障预测的机器学习算法。它还指示CMS在需要时触发数据,基于HA发送的数据。

日志记录器(DL)也可以存储所有相关数据,以便与其他容错方法的结果进行比较和分析。

2.数据源

来自嵌入式传感器内部数据提供有关设备状态的输入故障预测回写组件。由开发板中器件的具体情况,可以知道工作温度和直流变换器输出电压。如果知道变换器输出电压的波动或预期的温度上升,由于高过载或短路(当SEU影响路由资源),则可以预测即将发生故障,还可以实施新的探针在FPGA配置存储器,提供关于FPGA的逻辑元件的退化的有价值信息:监控开关元件在CLB延迟;捕捉它们的输出持续时间很短等问题。

外部信息可来自其他来源,如Web服务,提供关于太阳辐射爆发和环境条件(温度、湿度、压力等)的信息,或连接到FPGA的外部传感器(瞬时功耗等)。

3.系统验证

在第一阶段,系统会运行不同的工作负载和DL模块将采集的FPGA传感器数据到外部存储,该实验将重复几次,PM进行故障注入,使用故障注入器进行可重构嵌入式设备。然后进行相关分析:一是收集的传感器数据;二是所引入的配置内存错误;三是检测到的系统故障。在系统有故障信号时的PM输出不同于一个试验输出 (无故障注入实验),利用所采集的数据对机器学习算法进行训练并将其投入运行。当它预测一个即将发生的由于一个错误或长时间的延迟或多个交互错误累积的故障时,允许触发PM的完全回写。然后,将建议的方法与PM的非回写实现和定期的一次回写实施,不同的回写频率进行比较。这些方法的可靠性评估将使用故障注入进行。

四、结束语

在本文中,基于故障预测提出了一种新的方法,以提高FPGA的性能,通过自适应回写,能考虑到嵌入式传感器的设备正确信息,以及外部环境数据,而不是周期性地对一个永久的时间侵扰,消耗更多的功率。

参考文献:

[1]JUNMIN WU,XIAODONG ZHU,TAO LI,XIUFENG SUI,WBSP:A NovelSynchronizationMechanismforArchitectureParallelSimulation[J].ComputersIEEETransactionson.2016(65):992-1005.

[2]CHRISTIAN BIENIA,KAI LI.Fidelity and scaling of the PARSECbenchmark inputs[J].Workload Characterization (IISWC)IEEE InternationalSymposiumon,2010:1-10.

[3]DAVY GENBRUGGE,STIJN EYERMAN,LIEVEN EECKH OUT.Interval simulation:Raising the level of abstraction in architectural simulation[J].High Performance Computer Architecture(HPCA)2010IEEE16th International Symposium on.2010:1-12.

[4]蒋毅.IP路由器原理与技术[M].西安:西北工业大学出版社,2012:242-244.

[5]胡先志,刘一.光纤通信概论[M].北京:人民邮电出版社,2012.

[6]袁健.现场可编程门阵列(FPGA)技术在航空电子中的应用初探[J].航空电子技术,2016(1):15-19.

[7]茅靖峰,申海群,顾菊平,等.Lab VIEWFPGA实时仿真在现代电力电子技术实验教学中的应用[J].实验室研究与探索,2016(9):108-113.