基于FPGA和Nios II软核的纸张测量装置

张国亮,刘恒,李建勋,董千恒,路家琪

(南京信息工程大学电子信息与工程学院,江苏南京,210044)

0 引言

随着时代的发展,纸张已经广泛应用于人类生活的各个领域。但随着纸张的广泛应用,纸张测量计数问题亟需解决方案,目前常见的纸张测量的方案:一是用FDC2214电容传感器测量纸张电容,通过数据拟合来获得纸张数量[1]。虽然该方法案传感器得到的数据快速准确,但是振荡范围较小,若超出上限,则无法测量。二是利用多谐振荡器再通过单片机测频率[2],此类方法虽然对测量电容大小没有限制,但是测量频率的方法通常为测周法和测频法,这两种测量频率的方法极易引入误差,测量的精度不如第一种方案。结合上述背景,本文以FPGA为控制核心,Nios II软核为运算核心,从NE555振荡电路电容与的频率对应关系,通过等精度频率测量和数字滤波等算法,精确测量纸张数量并实时显示和语音播报当前纸张数量,提高了测量的量程、精度以及鲁棒性。

1 原理分析及计算

1.1 纸平行板电容器的理论分析

平行板电容器由两块相互平行的导体极板,中间夹以电介质构成,结构如下图1所示。平行板电容器的电容量与两导体极板之间的相对面积s和电介质材料的相对介电常数εr成正比,与两极板间距离d成反比。平板电容器电容的计算公式如下:

图1 平行板电容器模型

式(1)中:s为两导体极板的相对面积;ε0为真空介电常数;εr为相对介电常数(取决于电介质特性);d为两导体极板的绝对距离。

假如将纸张(此处使用得力70g的A4纸)填入两导体极板作为电解质,则该平行板电容器,则变为纸电容器,同理式(1)中的d即为纸张厚度,εr为纸张的相对介电常数,当填入不同纸张数量时式(1)中的相对面积s,真空介电常数ε0,相对介电常数εr均为固定值,则该电容器的电容值仅取决于纸张的厚度,即纸张的数量。

1.2 多谐振荡器理论分析

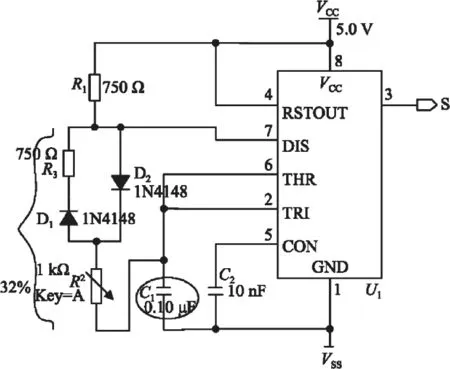

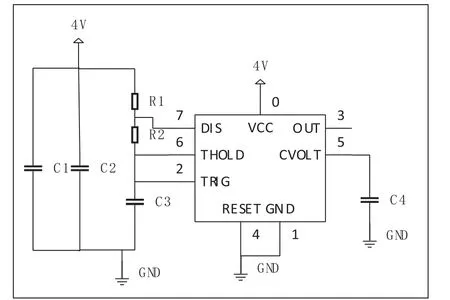

多谐振荡器电路包括固定电阻R1、R3,电容C1、C2,二极管D1、D2,可变电阻R2及NE555芯片,电源为+5V,电路如图2所示。

图2 多谐振荡器电路图

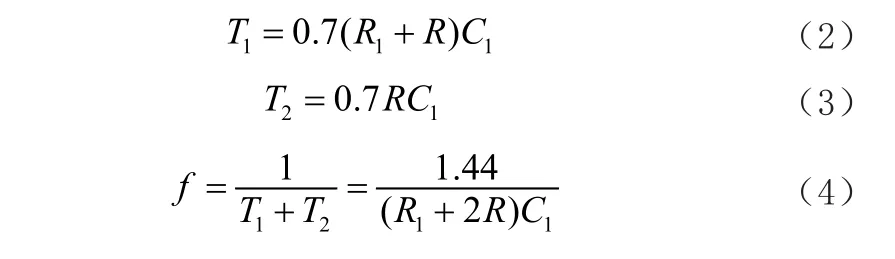

图2中,电阻R2、R3及二极管D1、D2构成等效电阻R。调节可变电阻R2和电容C1即可改变输出方波的频率,其中电路输出的方波高、低电平时间为T1和T2,周期为f,有:

根据上述原理只需改变电容C1的值就可改变输出方波的频率,方波高电平为+5V,低电平为0V,方波从S端输出[3]。

1.3 等精度频率测量理论分析

现有测频式纸张测量装置,测量频率的方法为测频法和测周法,当待测信号频率较低时采用测周法,当待测信号频率较高时采用测频法。测周法的误差主要来源于基准时钟信号和计数值,其次在闸门开始时,计数器不一定开始工作。测频法的误差主要来源于闸门时间,并且测量频率越低相对误差越大,实际工程中常将两种方法结合来使用,但精度依旧不能满足该类装置的要求。

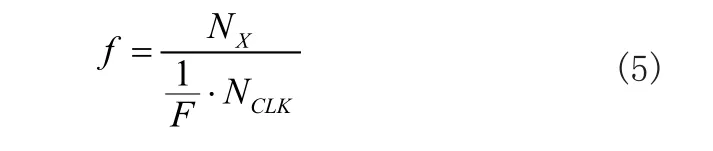

相较于上述两种测量频率的方法,等精度频率测量的最大特点是门控信号不唯一,门控信号是随着被测信号频率改变而改变的,该方法不仅测量精度高,而且在所有频率测量精度都一样,满足本装置的要求。在实际测量时,只需要将待测信号接入FPGA,利用D触发器将待测信号打两拍,异步信号转为同步信号,然后FPGA两个计数器开始计时工作,计数器1采集待测信号的上升沿数,计数器2采集此时的时钟信号的上升沿数。当计数器1计数到NX时,计数器1、2同时停止工作,此时计数器2的计数值为NCLK,假设FPGA的时钟频率为F,则待测信号的频率计算:

2 系统方案

将两块金属极板分别粘贴在两块亚克力板上,并保持金属板上下对齐,将一定数量的A4纸放入两极板并夹紧,FPGA对当前多谐振荡器频率的输出信号进行采集运算,计算出的谐振频率通过串口通信,送给FPGA内部的Nios II软核进行数据的处理和分析,最终能够计算出当前的电容值和纸张数量以及判断当前电容是否短路,并将结果显示在TFT屏幕上,同时将分析所得结果传输给FPGA,通过FPGA驱动语音播报模块,进行实时语音播报。测量装置如图3所示。

图3 测量装置总体框图

3 系统设计

3.1 系统实物结构

将两金属极板粘在两块亚克力板的相同位置上,再将两块亚克力板对齐,再亚克力板的四角钻孔,利用铜柱固定两块亚克力板的相对位置,使得每次测量时极板的相对位置不发生改变,同时将亚克力板垫高,远离桌面避免噪音以及电磁干扰。两金属极板通过SMA射频头连接屏蔽线接入图7的NE555多谐振荡器中,多谐振荡器中R1=R2= 2 00KΩ,TFTLCD通过排母接入FPGA,语音播报模块通过杜邦线与FPGA相连,最终构成了整个系统。

3.2 硬件设计

3.2.1 FPGA

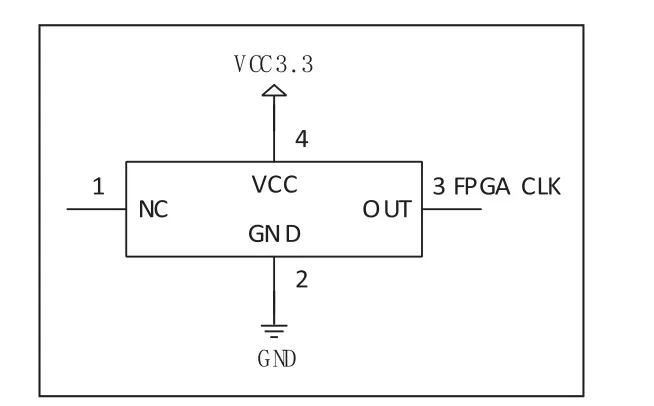

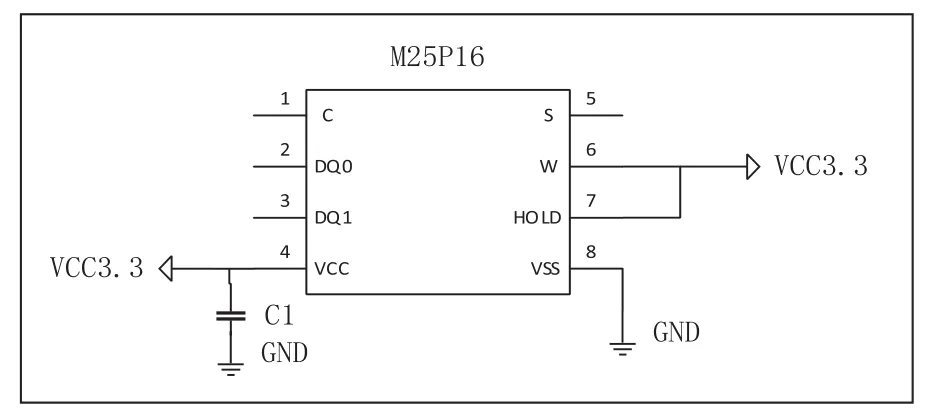

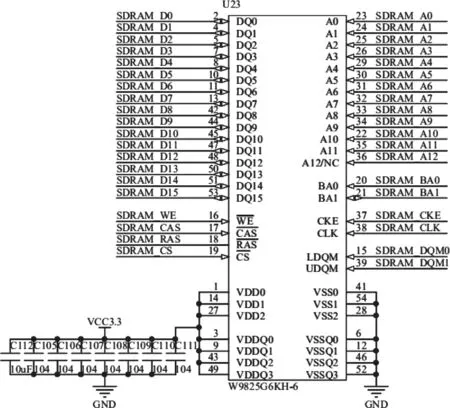

本装置选用ALTERA公司的Cyclone IV系列FPGA,具体芯片型号为EP4CE10F17C8,如图4所示FPGA的时钟为50MHz,搭载了FLASH、SDRAM等丰富的外设资源。如图5和图6所示,FPGA外接了M25P16芯片和W9825G6KH芯片,M25P16芯片是一款带有先进写保护机制和高速SPI总线访问的2M字节串行Flash存储器,W9825G6KH芯片是一款256M字节的DDR存储芯片,以上两个芯片为FPGA运行Nios II软核奠定了基础。

图4 FPGA时钟

图5 FLASH原理图

图6 SDRAM原理图

3.2.2 多谐振荡器

本文装置多谐振荡器原理图如图7所示,该电路以NE555为核心,包括电阻R1、R2及电容C1、Cx,其中中Cx为待测的纸电容器。纸电容器两端通过射频线接入电路中。图7电路在图2的基础上进行了简化,并在电源与地之间增加了105电容和104电容,通过两个电容对电源进行滤波,滤掉电源的高频杂波,消除了输出方波上升沿时的毛刺,便于后续FPGA对输出波形频率的计算。

图7 多谐振荡器原理图

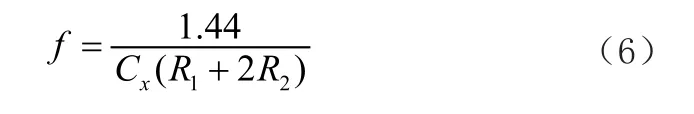

由于R1,R2为定值,则可由式(6)得出,多谐振荡器的振荡频率仅由纸电容器电容值所决定。由式(1)、(6)式得:

由式(7)得:多谐振荡器的振荡频率与纸张数成正比。已知一张A4纸的厚度约为,在理想条件下,忽略纸张之间空隙的影响,可求得电容器每怎加一张纸,其电容上升2.77× 10-9F,振荡器频率约增加866Hz 。

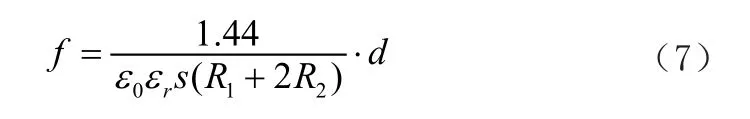

3.2.3 TFTLCD屏

本装置选用4.3寸TFTLCD电容屏其接线方式如图8所示,通过FPGA的Nios II软核驱动该屏幕,在屏幕上显示当前谐振频率和纸张数量,当两极板短接时会显示报警信息。

图8 TFTLCD接线方式

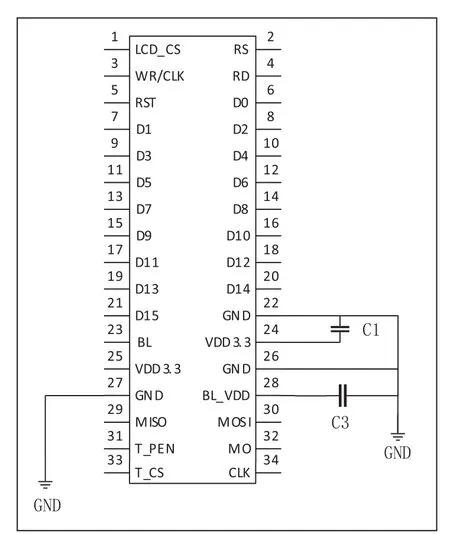

3.2.4 语音播报模块

本装置选用了以VS1053B芯片为核心的语音播报模块,该模块的电路如图9所示。当Nios II软核将数据传输给FPGA后,FPGA可以驱动该模块播报当前谐振频率和纸张数量,当两极板短接时,会发出相应的语音提示。

图9 语音播报模块电路原理图

3.3 软件设计

3.3.1 系统软件设计

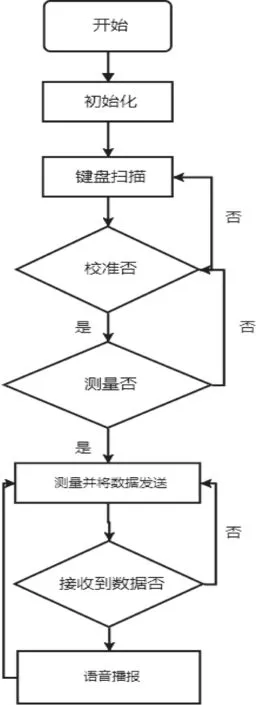

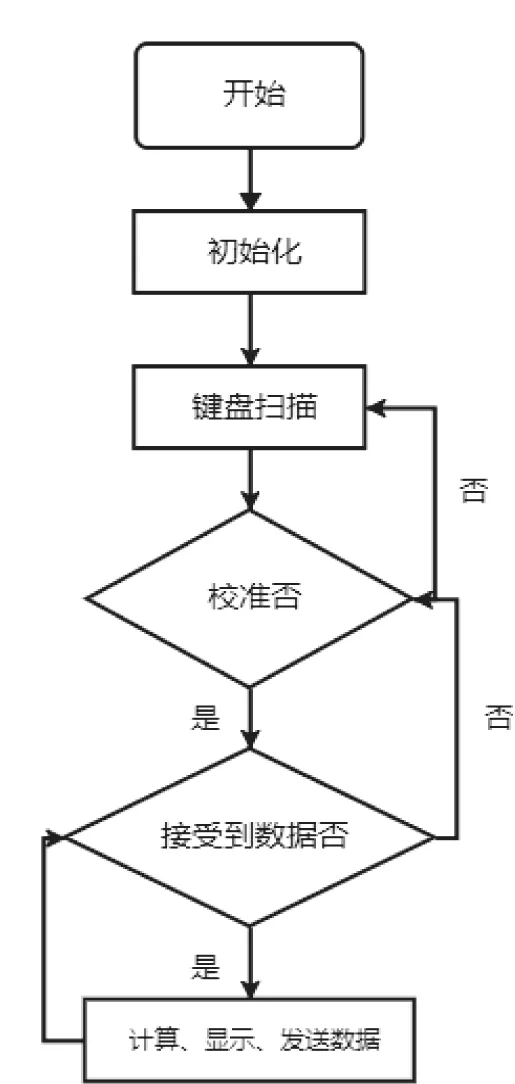

本软件设计是在quartus II环境下,用Verilog和C语言进行编写的,FPGA工作流程如图10所示,Nios II软核工作流程如图11所示。

图10 FPGA工作流程图

图11 Nios II软核工作流程图

软件的工作流程:系统上电后,所有功能模块初始化,当功能初始化结束,接着通过按键进行自检验校准,防止不同环境温湿度对纸张测量结果的影响。校准完成后,将校准数据进行存储,并以校准数据制作查找表用以判断相同规格的纸张的数量。正式测量时,将某一数量的纸张放入两极板内压紧,之后FPGA将进行等精度频率测量,测量结束后将测量所得的频率值传输给Nios II软核进行浮点数计算,Nios II计算完后将直接驱动TFT显示当前纸张数量,同时将数据传输给FPGA用以驱动语音播报模块进行纸张数量播报或发出报警。

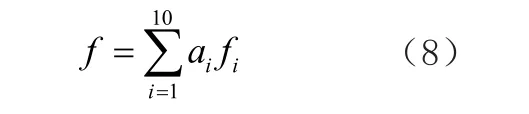

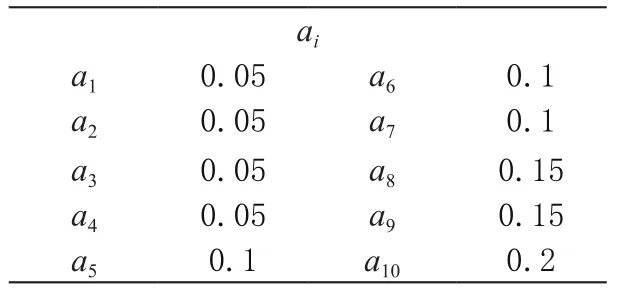

3.3.2 卡尔曼数字滤波

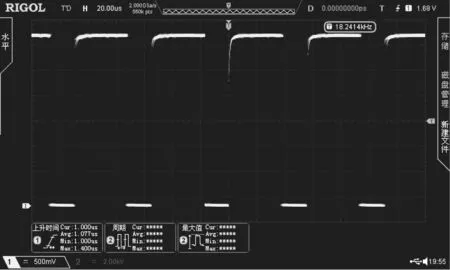

由于实际制作的纸电容器具有边缘效应等情况,Cx的值是一个波动的值,则多谐振荡器的谐振频率也是一个不稳定的值,其波形如图12所示。频率不稳定,则会影响校准和测量的结果,为了避免这一现象对数据的影响,在数据计算时采用了卡尔曼数字滤波算法,利用FPGA采集10次谐振频率,频率值用f(ii为采集次数)来表示,fi对应权重为ai,ai取值见表1。处理后的谐振频率表示如下:

表1 权重ai的取值

图12 多谐振荡器实际输出波形

4 测试

4.1 正常环境测试

在室温条件下,将一定数量的A4纸放入两极板中并夹紧,测量区间为1-90张纸,读取TFT屏幕上的数值或者记录语音播报的数值,同时读取示波器上的频率,将1-90张纸的部分数据以及误差分析依次计入到表2中,经过测试本装置在1-90张纸内最大测量误差为1.18%,在91-150张纸的最大测量误差为4.02%。

表2 室温下测量结果及误差分析

测试结果分析:当纸张数逐渐增加时,多谐振荡器的谐振频率也逐渐增加,但当纸张数量超过一点程度时,虽然依旧呈现上升趋势,但是线性分布以及不够明显。由式(3)可得,频率应该与纸张数量成正比,但是由于纸张的边缘效应等客观因素,实际测试结果并非线性,但通过上述的卡尔曼数字滤波算法以及自检验的过程,测量1~90张纸的误差可以控制在1.18%以内。

4.2 装置抗干扰测试

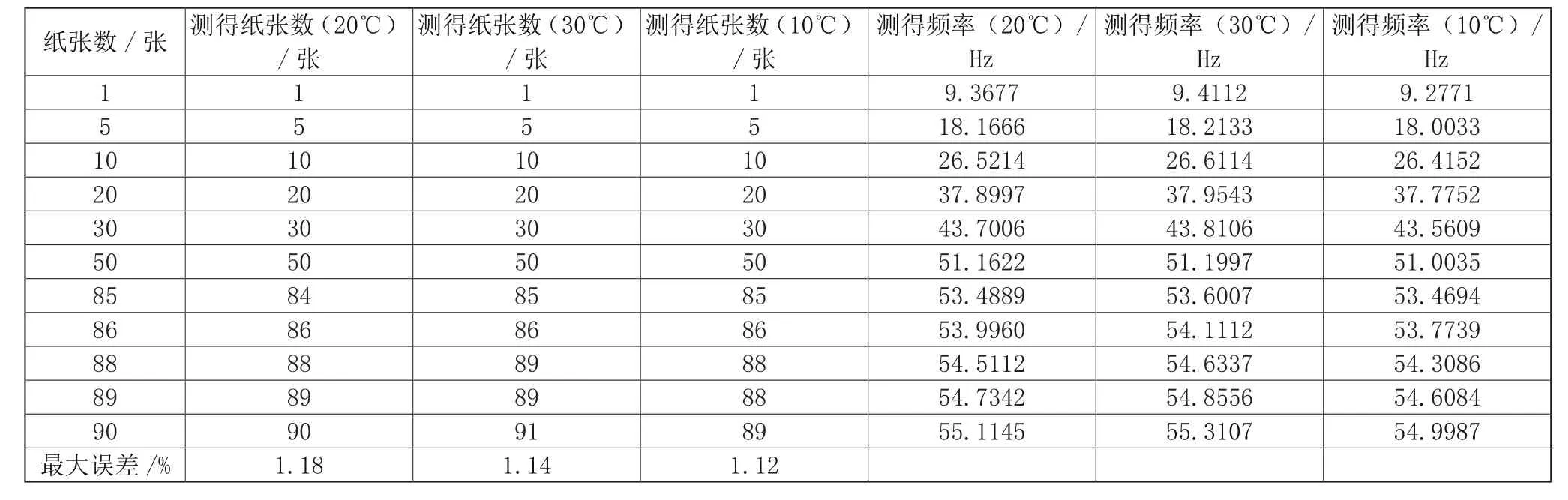

由于热涨冷缩原理,纸张的厚度在不同的温度下是不同的,所以装置的鲁棒性极为重要,于是将本文装置在恒温实验环境中测试,并将测试结果以及误差分析记录在表3中。

表3 不同环境测量结果及误差分析

由表3可得,本实验装置在不同环境下,相同纸张数测量的频率也略有不同。当环境温度高时,纸张由于受热膨胀,每张纸的厚度略有上升,FPGA测得的频率也相对偏高;当环境温度低时,纸张厚度略微降低,FPGA测得的频率也相对偏低。但最后实际计算出来的纸张数量误差依旧能够控制在1.18%,故本系统在90张纸的量程内,具有非常好的鲁棒性。

5 总结

基于FPGA和Nios II软核的纸张测量装置可以完成在一定规格的纸张测量任务,具有成本低,速度快,误差小,量程广,鲁棒性高的优点。但由于纸张的边缘效应等导致纸张数量到达一定程度时,线性度不明显,这一问题对后续纸张测量精度影响较大。这个问题我们会在后续的研究中进一步改进。