一种摆率可控的PD发射机模拟前端电路的设计

金克庆, 刘兴辉, 赵建中, 李 智

(1.辽宁大学 物理学院,辽宁 沈阳 110036; 2.中国科学院微电子研究所 感知中心,北京 100029)

对于PD发射机的设计,文献[5]采用2个不同电容进行充放电的摆率控制方式,具有一定的抑制EMI的作用,但由于充放电回路采用不同电容,易受制造工艺偏差影响,很难保证PD信号稳定的边沿时间;文献[6]在文献[5]的基础上进行了改进,虽然通过迟滞结构与修调的方法提升了边沿精度,但仍然无法解决充放电电容不同带来的工艺偏差的影响;文献[7]采用由时钟控制的开关电容延迟电路的方案,虽然可以做到边沿时间精确控制,但采用修调电容的形式依然会存在工艺偏差的影响且输出波形抗干扰能力较差。基于此,本文采用同一电流双路对称镜像进行单电容充放电的设计并通过调节电流的形式进行精确的摆率控制,能有效抑制制造工艺偏差造成的影响和较高摆率产生的EMI问题;宽电源范围的设计,能有效应对电源电压波动造成输出波形畸变的问题;输出级采用高增益两级放大器以保证驱动CC线缆的能力。

1 EMI问题和电磁兼容性分析

USB PD协议常与Type-C接口配合使用,典型的24引脚 Type-C接口包含CC1和CC2共2个检测和通信引脚。除上述的2个引脚外,其还具有高速引脚[8],特点是高速信号通信和电源通信均使用同一个连接器。

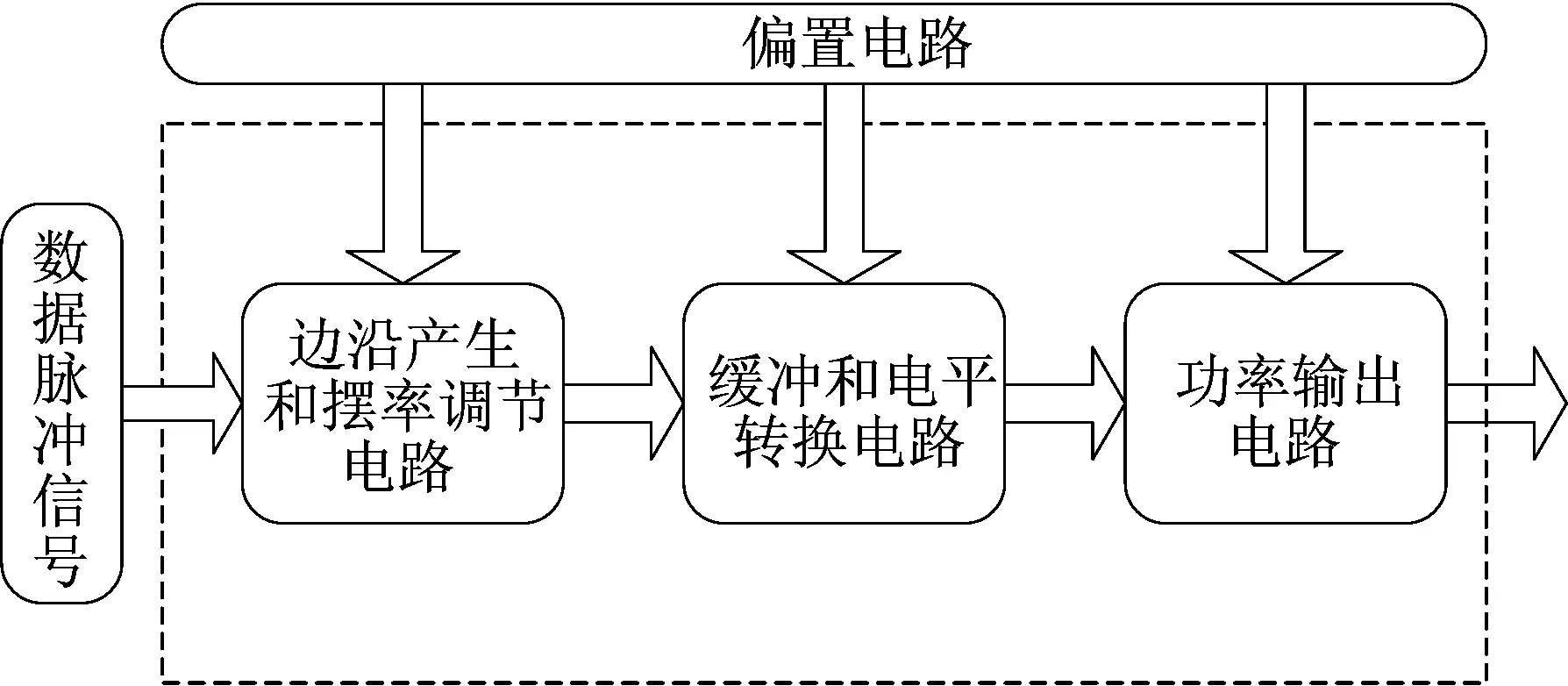

由信号与系统理论可知,任何信号都可分解成不同频率的正弦信号的组合。根据傅里叶分析,当一周期信号满足狄里赫利条件,即在一个周期内,周期信号必须绝对可积,存在有限个极值点,且存在有限个间断点[9],则其可以展开成傅里叶级数形式,即

(1)

其中:a0、ak为系数;φk为相位;ω1=2π/T,T为周期。因此周期性方波信号的傅里叶级数为:

(2)

其中,Vtop为信号幅值。

由式(2)可知,方波信号可由正弦信号的基波与其奇次谐波叠加产生,且谐波个数越多越接近理想方波,为19次谐波叠加而成的方波信号,如图1所示。

图1 19次谐波叠加而成的方波信号

由吉布斯效应可知,在方波的转折处将出现一定的振铃现象,这不利于信号的传输[10]。因此,PD通信中若CC接口上传输的信号摆率过高,产生的高次谐波的幅度也会越大,其可通过线缆耦合到Type-C接口的其他传输线中,会对其他高速数据信号产生EMI而出现电磁兼容性(electromagnetic compatibility,EMC)问题导致通信失败。于是适当缓的信号摆率可以减小高次谐波分量和幅度,有助于抑制EMI问题而保证信号完整性[11-12]。合理的摆率控制是PD正常通信的重要前提,USB PD 3.0协议规范了其发射机信号的边沿时间和高低电平[13]。要求CC线缆上传输信号的高电平VH为1.050~1.200 V,低电平VL为-0.075~0.075 V,上升时间tR和下降时间tF皆大于300 ns。

1) 实测桩土界面的土压力和孔隙水压力.目前研究主要是针对桩周土压力和孔隙水压力进行测试,而桩土界面是桩土体系的关键,桩土界面有效径向压力的变化规律有待研究.

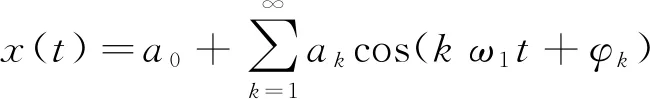

2 PD发射机模拟前端电路的设计

PD发射机模拟前端整体电路框图如图2所示。主要由边沿产生和摆率调节电路、缓冲和电平转换电路、功率输出电路3个部分组成。基本工作原理为偏置电路分别给PD发射机模拟前端电路的3个子模块提供偏置电压和偏置电流,数据脉冲信号加到边沿产生电路来控制电容充电或放电过程,其配合摆率调节电路输出稳定的、摆率可控的信号,经过缓冲和电平转换电路转换为峰值为1.125 V的信号,再经过功率输出电路输出稳定的、具有强驱动能力的PD通信信号。

图2 USB PD发射机整体电路框图

2.1 边沿产生和摆率调节电路

边沿产生和摆率调节电路如图3所示。采用同一电流双路对称镜像的方式进行单电容充电或放电过程,充放电回路采用同一电容保证了信号上升和下降的摆率恒定,既可以有效抑制传统结构中不同电容由于制造工艺偏差导致边沿时间不对称的影响,也可以抑制信号摆率过高而产生EMI现象导致的EMC问题;同一电流镜像的设计可以防止脉冲数据信号直接施加到开关上出现充放电回路同时导通或同时关断的状态而引发信号瞬间上拉或下拉导致输出波形畸变的现象,保证了信号的稳定性。

图3 边沿产生和摆率调节电路

工作原理如下:V1.5为线性稳压器提供的1.5 V偏置电压,基准电流Ibias为电路提供偏置电流。当数据脉冲信号低电平时,up为低电平,down为高电平, M15导通,M16断开,M17、M18均为二极管连接,A点电压升高,B点仍为低电平,M9导通,M10断开,基准电流Ibias通过M13、M14组成的电流镜结构为M14提供的电流经由M15后通过M17、M9,M1、M2组成的电流镜结构镜像到M2,形成V1P5到C1的通路,进行充电过程,直至C1两端电压充到1.5 V为止;当数据脉冲信号高电平时,up为高电平,down为低电平,M15断开,M16导通,A点为低电平,B点电压升高,M10导通,M9、M1、M2均断开。Ibias通过M13、M14组成的电流镜结构为M14提供的电流经由M16后再通过M18、M10组成的电流镜镜像到M10,C1通过M10形成对地通路,进行放电过程,直至放电完成为止。电容电流计算公式为:

(3)

由式(3)可得:

(4)

其中:kslew-rate为充放电斜率,即摆率;C为电容容量;I为电流;Δu为电压的变化量;Δt为时间变化量。由于电容的容量不变;Δu的变化恒定,选取10%~90%的振幅点为边沿时间,因此,可以通过改变充放电电流I调整边沿时间进行摆率调节。

摆率调节单元由M3、M4、M5、M6、M7、M8、M11、M12组成。通过2个修调信号SR〈1〉、SR〈0〉控制是否增加充放电通路来进行边沿时间调节,以应对制造工艺的偏差,达到稳定可靠的、可供CC线缆识别的PD信号的目的。

2.2 缓冲和电平转换电路

为适应工艺偏差的影响,设计了由差分放大器和源极跟随器组成的缓冲和电平转换电路,如图4所示。

图4 缓冲和电平转换电路

图4中:第1级由M21、M22、M23、M24、M25、M26组成双入单出差分放大器;第2级由M27、R1、R2组成源极跟随器。

工作原理为:偏置电流Ibias通过M19镜像到M28、M20,为其支路提供电流;VE为M23、M24提供偏置电压。忽略衬底偏置效应、寄生等因素,由式(5)~(8)可以推出式(9),即

Av1=gm22[ro22‖(gm24ro24ro26)]

(5)

(6)

(Vslew-VD)Av1Av2=VD

(7)

(8)

(9)

其中:Av1为差分放大器的开环增益;Av2为源极跟随器的开环增益。通过合理调节MOS管宽长比和电阻R1、R2的比值可以实现输出峰值为1.125 V的PD信号,比例电阻的形式消除了工艺上电阻偏差的影响。

2.3 功率输出电路

为保证PD信号稳定工作,考虑到CC线缆的寄生等因素,功率输出电路采用全差分结构和电流镜作负载的差分转单级放大器组成高增益两级放大器,且接成单位增益缓冲器的形式。功率输出电路如图5所示,M44、M45采用大宽长比的MOS管,保证了强驱动能力,高增益两级放大器保证了跟随电压的精度。

图5 功率输出电路

工作原理为:偏置电流Ibias通过M31镜像到M32、M35,为其支路提供电流。两级放大器的第1级为由M36、M37、M38、M39、M40、M41组成的全差分结构,采用2个同样宽长比且工作在线性区的M40、M41组成串联电阻并接在输出端以读取输出电压,并将采样中间点接到M38、M39的栅极来组成共模反馈电路,解决了电流源作为负载的全差分结构输出共模电平无法确定的问题,VF为M40、M41的栅极提供偏置电压,M41的等效阻抗计算公式为:

(10)

第2级由M42、M43、M44、M45组成双入单出差分放大器,设M44与M42的宽长比为M,忽略寄生等因素,可得:

Av3=gm37(ro41‖ro37‖ro39)

(11)

(12)

(13)

其中:Av3为全差分放大器的开环增益;Av4为双入单出差分放大器的开环增益。

当M45工作在线性区时,式(12)中ro45变为ron45,结果类似式(10)。

3 电路仿真结果

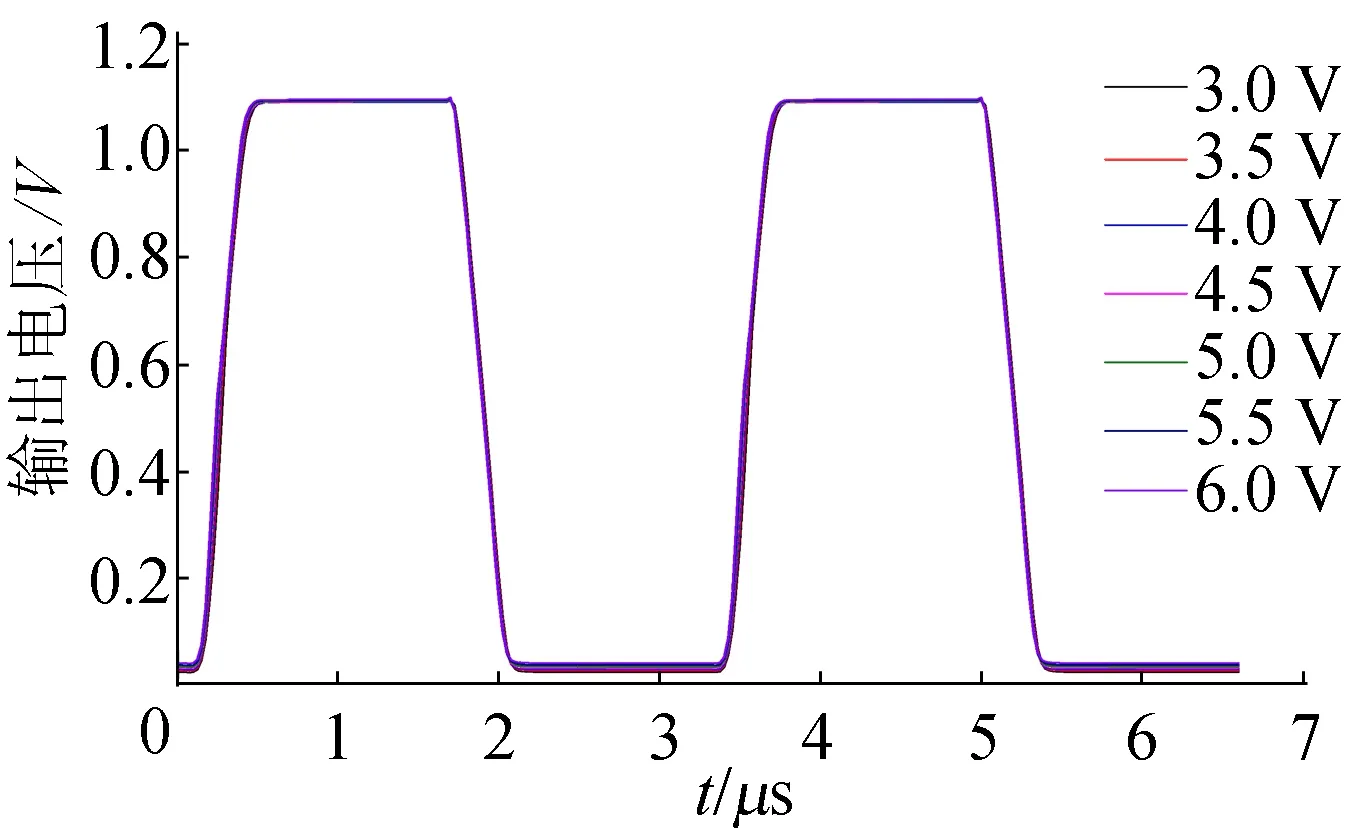

本文采用HHGRACE 0.35 μm BCD工艺设计,采用Spectre和Hspice进行仿真验证。输入频率为300 kHz的脉冲信号,输出负载为线缆电感为640 nH、电容为1 280 pF。

设计中通过调节MOS管的过驱动电压进行宽电源范围设计,以应对电源电压波动造成输出波形畸变的问题,具有良好的稳定性。电源电压以0.5 V为步长,从3~6 V进行瞬态仿真,仿真波形如图6所示。从仿真结果可以看出输出信号波形几乎无偏差,高电平均在1.05~1.20 V之间,低电平在-0.075~0.075 V之间,结果见表1所列。

表1 不同电源电压下的高低电平 单位:V

图6 不同电源电压下的输出波形

图7 摆率修调波形

本文通过两位编码进行摆率修调(trim),摆率修调波形如图8所示,修调精度见表2所列。

表2 摆率修调(trim)精度 %

图8 电路版图布局

电路版图布局如图8所示,数据脉冲输入信号置于左上,方便接入;缓冲和电平转换电路置于左上;边沿产生和摆率调节置于左下,其中充放电电容置于版图中间以减小干扰;功率输出级置于右半部分,其中输出管尺寸较大,置于右下方便连接负载。通过以上设计,减小了芯片面积、走线长度、寄生电容和电阻等。

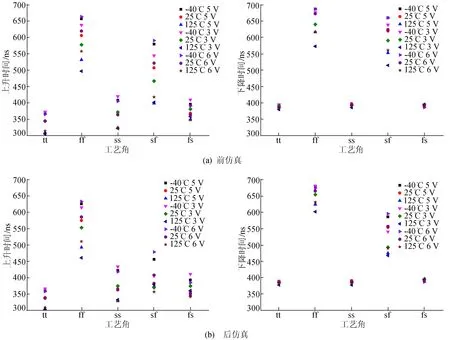

在温度为-40、25、125 ℃,电源电压为3、5、6 V,工艺角为tt、ss、ff、sf、fs下,分别采用Spectre和Hspice进行前、后仿真,仿真结果统计如图9所示,前后仿真结果整体相差不大,只在sf工艺角下有一定偏差,整体边沿时间均在300~700 ns之间,满足USB PD3.0协议标准要求。

图9 边沿时间前、后仿真统计结果

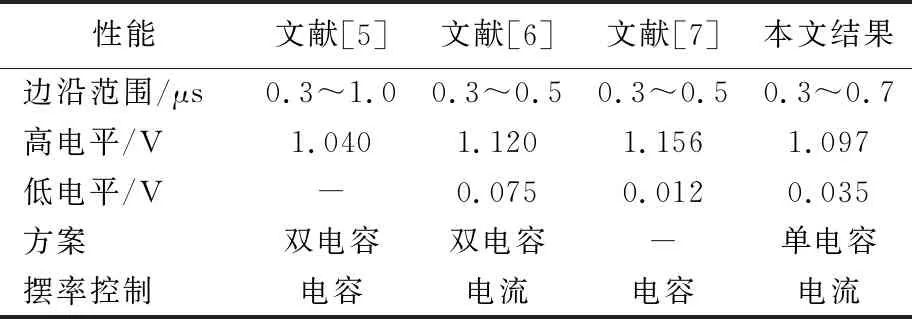

本文从边沿范围、摆率控制等方面与已有方案进行了对比,结果见表3所列。通过对比可以看出,本文采用的单电容方案避免了电容不同的偏差,修调电流的方式具有精度高、且不易产生波形畸变,抗干扰性好的特点。

表3 不同方案性能的对比

4 结 论

本文设计了一种摆率可控的PD发射机模拟前端电路,满足USB PD 3.0协议标准。对于PD通信中的EMI问题有很好的抑制作用,单电容的设计规避了传统不同电容方案带来的稳定性问题的影响;同一电流双路对称镜像结构能有效抑制波形畸变问题,宽电源范围的设计能更好地适应电源电压波动;两级运放作为输出级能提供大的线缆驱动能力,具有非常好的适用性。