基于J750EX测试系统的SDRAM测试技术研究

王征宇,何志伟,章少云

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

基于J750EX测试系统的SDRAM测试技术研究

王征宇,何志伟,章少云

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存储器)以其卓越的性能、低廉的价格得到了广泛的应用,但由于此类器件具有容量较大(通常为百兆级及以上)、对其实施控制较复杂等特点,使得SDRAM的测试也存在较高难度,因此,探索SDRAM的测试技术,并创建该类器件的测试平台也具有十分重要的意义。首先介绍了SDRAM的基本工作原理,其次详细阐述了基于J750EX测试系统的测试技术研究,提出了采用J750EX系统的DSIO资源实现SDRAM地址累加生成的方法,大大减少了测试矢量长度,可以有效节省测试开发时间,降低测试成本。另外,针对SDRAM的关键时序参数,如tRCD(行选通周期)、CL(读取潜伏期)、tWR(写回时间)等,使用测试系统为器件施加适当的控制激励,完成SDRAM复杂的时序配合,从而达到器件性能的测试要求。

同步动态随机存储器;DSIO;J750EX

1 概述

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存储器)因其具有容量大、高速、价格低廉等特点,在业界得到了十分广泛的应用,是内存家族中尤为重要的一员。由于SDRAM通常具备较大的容量(百兆级及以上),且对其实施控制、完成相应的功能操作较为复杂,使得对该类器件的测试也存在较高难度。本文介绍了一种基于Teradyne公司的J750EX测试系统来实现对SDRAM性能评价的测试方案。

2 SDRAM的基本工作原理

SDRAM在基本原理上,比如基本存储的结构都是大致一样的,但是在整个内存架构的组织上是不同的,而且在存储单元的控制上也有相当大的区别,本文以Micron公司的MT48LC4M32B2为例,简要介绍SDRAM的基本工作原理。

2.1 MT48LC4M32B2的引脚定义

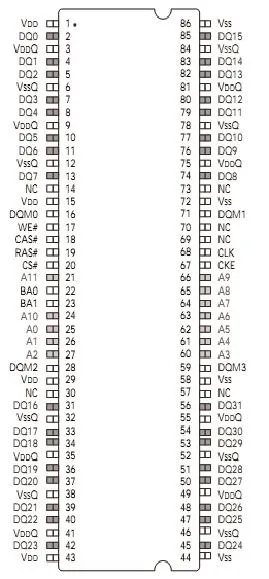

图1显示的是MT48LC4M32B2 128 Mb SDRAM的引脚示意图,它采用了86 pin TSOP封装。电路的各个引脚定义如下(下列管脚名称中,标有“#”标记的表示在低电平下有效):

(1)A0~A11:地址输入引脚,当执行ACTIVE命令和READ/WRITE命令时,来决定使用某个bank内的某基本存储单元。

(2)CLK:时钟信号输入引脚,SDRAM所有输入信号的逻辑状态都需通过CLK的上升沿采样确定。

(3)CKE:时钟使能引脚(Clock Enable),高电平时有效。CKE信号的用途有两个:一、关闭时钟以进入省电模式;二、进入自刷新状态。CKE无效时,SDRAM内部所有与输入相关的功能模块停止工作。

(4)CS#:芯片选择(Chip Select),为输入信号,低电平有效。只有当片选信号有效后,SDRAM才能识别控制器发送来的命令。

(5)RAS#:行地址选择(Row Address Select),为输入信号,低电平有效。

(6)CAS#:列地址选择(Column Address Select),为输入信号,低电平有效。

(7)WE#:写入信号(Write Enable),为输入信号,低电平有效。

图1 MT48LC4M32B2的引脚定义

(8)DQ0~DQ31:数据输入输出接口。

(9)BA0~BA1:Bank地址输入信号引脚,BA0、BA1信号决定了激活哪一个bank、进行读写或者预充电操作,也用于定义Mode寄存器中的相关数据。

(10)NC:空引脚。

(11)DQM0~DQM3:此引脚主要用于屏蔽输入/输出,功能相当于OE#引脚(Output Enable),高电平有效。当其有效时,数据总线上出现的对应数据字节被接收端屏蔽。

(12)VDDQ:DQ供电引脚,可以提高抗干扰强度。

(13)VSSQ:DQ供电接地引脚。

(14)VSS:内存芯片供电接地引脚。

(15)VDD:内存芯片供电引脚, 提供+3.3 V ± 0.3 V。

SDRAM具有多种工作模式,内部操作是一个复杂的状态机。SDRAM器件的引脚分为以下几类:

(1)控制信号:包括片选、时钟、时钟使能、行列地址选择、读写有效及数据有效。

(2)地址信号:行列复用引脚,根据行列地址选择引脚,控制输入的地址为行地址或列地址。

(3)数据信号:双向引脚,受数据有效控制。

2.2 MT48LC4M32B2的指令集

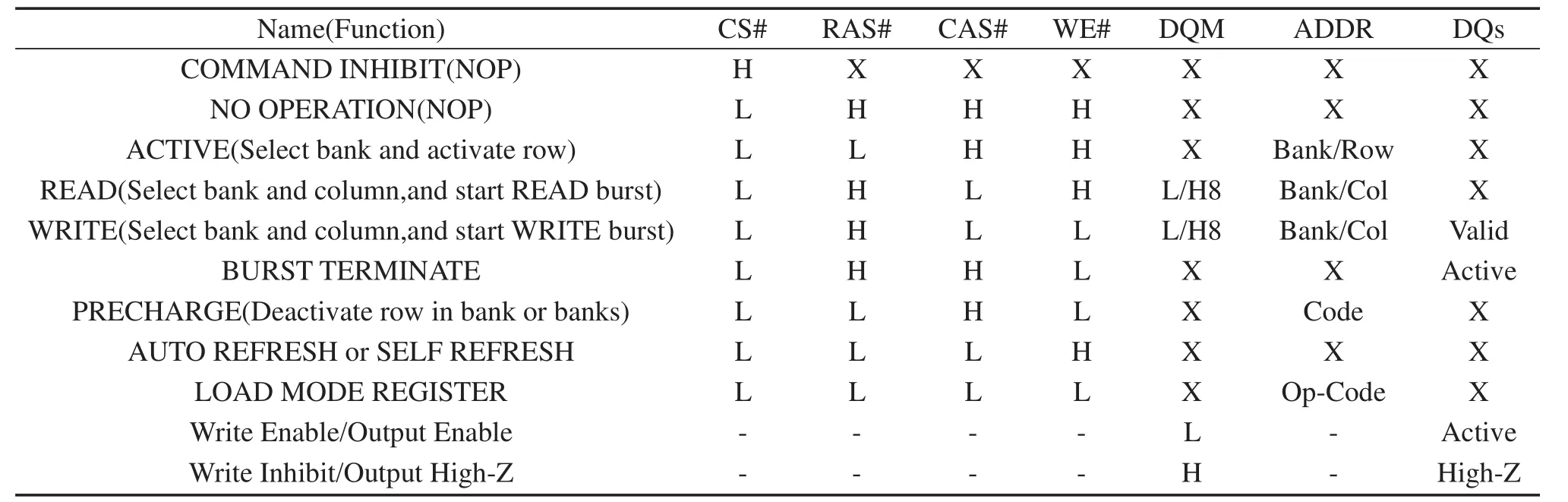

MT48LC4M32B2的所有操作都同步于时钟,根据时钟上升沿控制管脚和地址输入的状态,可以产生多种输入命令。表1列出了不同命令下各个引脚的信号。“H”代表高电平,“L”代表低电平,“X”代表可以是任何状态,即该引脚同该命令并没有直接的关系。

表1 MT48LC4M32B2指令集

从表1中可以看到,所有的操作命令均通过控制线CS#、RAS#、CAS#、WE#、DQM和地址线、数据线等输入,MT48LC4M32B2支持的操作命令有初始化配置、预充电、行激活、读操作、写操作、自动刷新、自刷新等。

2.2.1 行激活(ACTIVATE)

行激活命令选择处于空闲状态存储体的任意一个行,使之进入准备读/写状态。从体激活到允许输入读/写命令的间隔时钟节拍数取决于内部特征延时和时钟频率。MT48LC4M32B2内部有4个体,为了减少器件门数,4个体之间的部分电路是公用的,因此它们不能同时被激活,而且从一个体的激活过渡到另一个体的激活也必须保证有一定的时间间隔。

2.2.2 预充电(PRECHARGE)

预充电命令用于对已激活的行进行预充电,即结束激活状态。预充电命令可以作用于单个体,也可以同时作用于所有体(通过所有体预充电命令)。对于突发写操作,必须保证在写入预充电命令前写操作已经完成,并使用DQM禁止继续写入数据。预充电结束后回到空闲状态,也可以再次被激活,此时也可以进入低功耗、自动刷新、自刷新和模式设置等操作命令。预充电中重写的操作与刷新操作一样,只不过预充电不是定期的,而只是在读操作以后执行的。因为读取操作会破坏内存中的电荷。因此,内存不但要每64 ms刷新一次,而且每次读操作之后还要刷新一次。

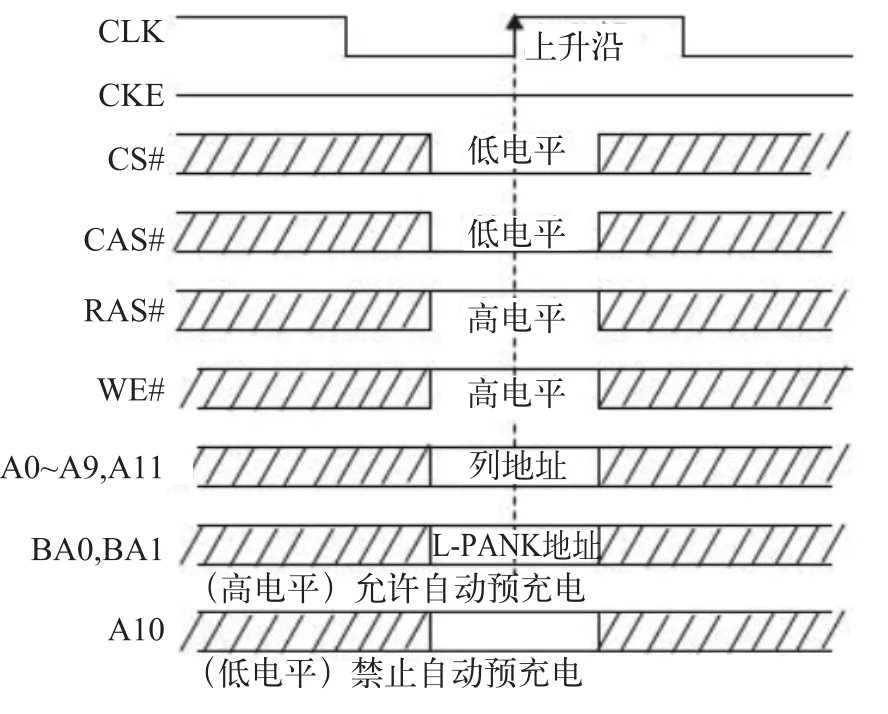

另外也可设置自动预充电,如果在突发读或突发写命令中,A10位置为“1”,在读写操作完成后自动附加一个预充电动作。操作行结束激活状态,但在内部状态机回到空闲态之前不能给器件发送新的操作命令。

2.2.3 突发读

突发读命令允许某个体中的一行被激活后,连续读出若干个数据。第一个数据在经过指定的CAS延时节拍后呈现在数据线上,以后每个时钟节拍都会读出一个新的数据。突发读操作可以被同体或不同体的新的突发读/写命令或同一体的预充电命令及突发停止命令中止。

2.2.4 突发写

突发写命令与突发读命令类似,允许某个体中的一行被激活后,连续写入若干个数据。第一个写数据与突发写命令同时在数据线上给出,以后每个时钟节拍给出一个新的数据,输入缓冲在突发数据量满足要求后停止接受数据。突发写操作可以被突发读/写命令或DQM数据输入屏蔽命令和预充电命令或突发停止命令中止。

2.2.5 自动刷新

由于动态存储器存储单元存在漏电现象,为了保持每个存储单元数据的正确性,MT48LC4M32B2必须保证在64 ms内对所有的存储单元刷新一遍。一个自动刷新周期只能刷新存储单元的一个行,每次刷新操作后内部刷新地址计数器自动加“1”。只有在所有体都空闲(因为4个体的对应行同时刷新)并且未处于低功耗模式时才能启动自动刷新操作,刷新操作执行期间只能输入空操作,刷新操作执行完毕后所有体都进入空闲状态。该器件可以每间隔15.625 μs执行一次自动刷新命令,也可以在64 ms内的某个时间段对所有单元集中刷新一遍。

2.2.6 自刷新

自刷新是动态存储器的另一种刷新方式,通常用于在低功耗模式下保持SDRAM的数据。在自刷新方式下,SDRAM禁止所有的内部时钟和输入缓冲(CKE 除外)。为了降低功耗,刷新地址和刷新时间全部由器件内部产生。一旦进入自刷新方式只有通过CKE变高才能激活,其他的任何输入都将不起作用。给出退出自刷新方式命令后必须保持一定节拍的空操作输入,以保证器件完成从自刷新方式的退出。如果在正常工作期间采用集中式自动刷新方式,则在退出自刷新模式后必须进行一遍(对于MT48LC4M32B2来说,4096个)集中的自动刷新操作。

2.2.7 时钟和时钟屏蔽

时钟信号是所有操作的同步信号,上升沿有效。时钟屏蔽信号CKE决定是否把时钟输入施加到内部电路。在读写操作期间,CKE变低后的下一个节拍冻结输出状态和突发地址,直到CKE变高为止。在所有的体都处于空闲状态时,CKE变低后的下一个节拍SDRAM进入低功耗模式并一直保持到CKE变高为止。

2.2.8 DQM操作

DQM用于屏蔽输入输出操作,对于输出相当于开门信号,对于输入禁止把总线上的数据写入存储单元。对读操作DQM延迟2个时钟周期开始起作用,对写操作则是当拍有效。

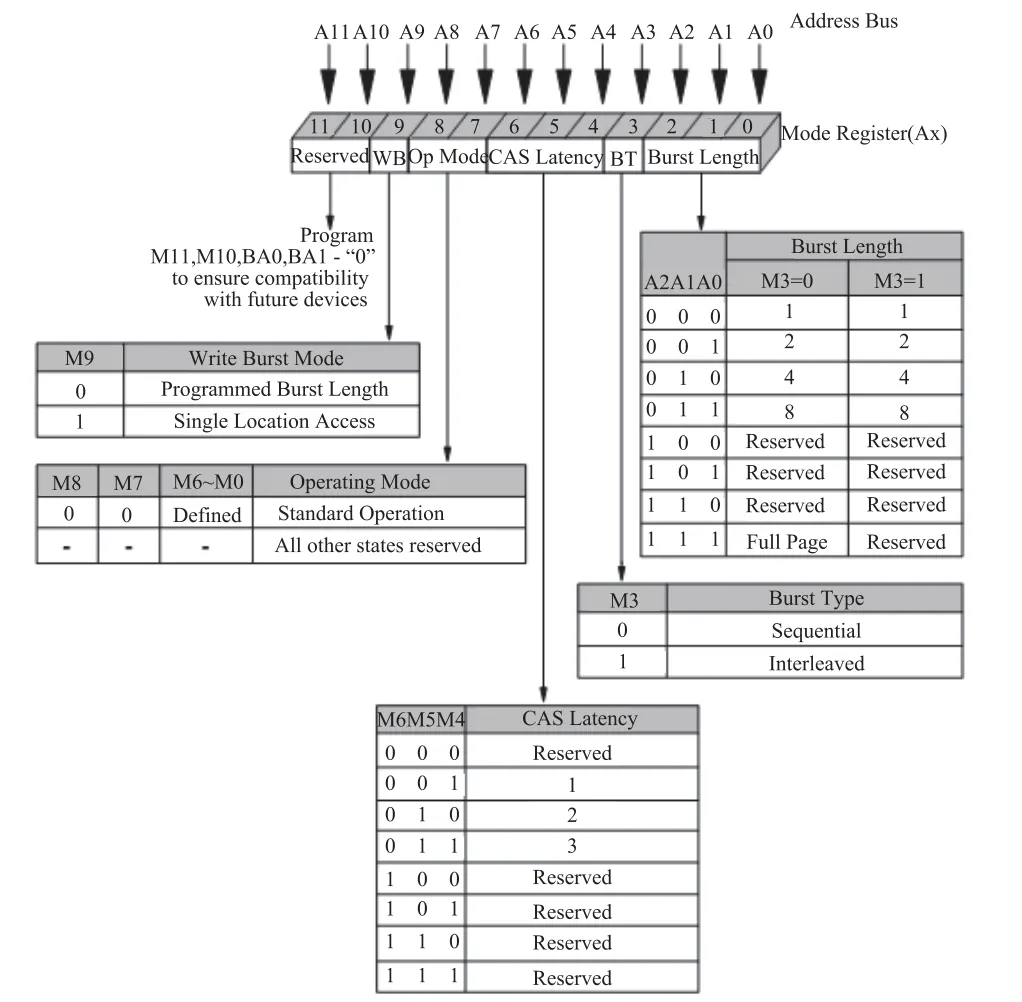

2.2.9 模式寄存器(Mode Register)

Mode Register用于定义MT48LC4M32B2运行的模式。其中包括了突发长度(burst length)、突发类型(burst type)、CAS延迟(CAS latency)、运行方式(operating mode)和写入突发模式(如图2所示)。

Mode Register通过LOAD MODE REGISTER命令进行编程,这组信息将会一直保存在Mode Register中直到内存掉电之后才会消失。Mode Register中的M0~M2用来定义突发长度(burst length),M3定义突发类型为连续的(sequential)或者交错的(interleaved),M4~M6定义CAS延迟,M7和M8定义运行模式,M9定义写入突发模式(write burst mode),M10和 M11目前保留。

Mode Register必须在所有的bank都处于idle状态下才能被载入,在所有初始化工作都进行完毕之前,外部控制器必须等待一定的时间。在初始化过程中发生了任何非法的操作都可能导致初始化失败从而导致整个计算机系统不能启动。

图2 模式寄存器(Mode Register)的定义

(1) 突发长度(Burst Length)

Read和write操作都可以通过突发模式访问MT48LC4M32B2,而突发模式的长度则是在初始化过程中载入模式寄存器中的参数设定的,这些参数当然是由厂商或者用户定义的。在图2中可以看到突发长度决定了READ或者WRITE命令能够访问的列地址的最大数目。

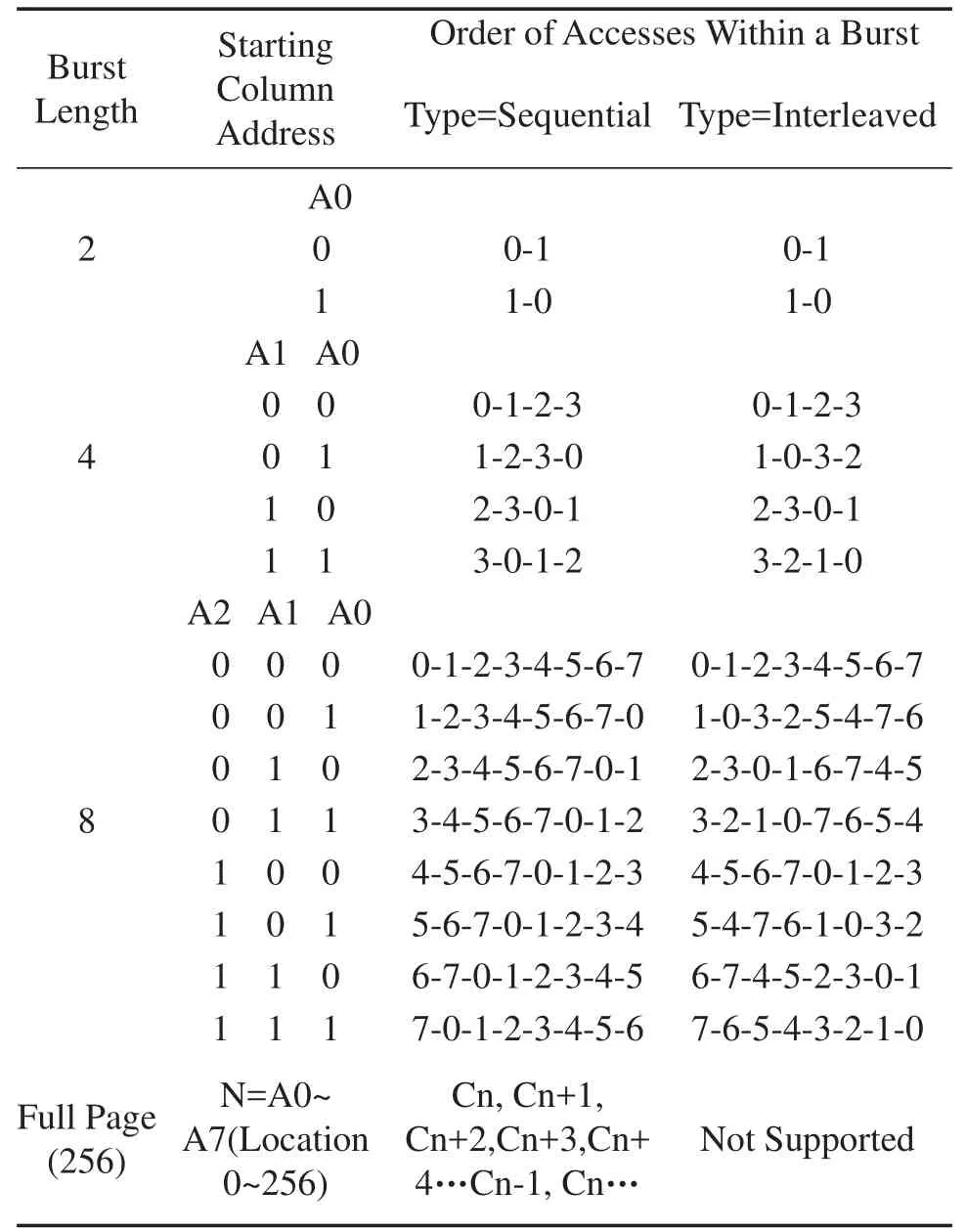

对于sequential和interleaved这两种突发模式,其突发长度是1、2、4、8,另外全页(full page)突发模式仅仅适用于sequential类型。全页突发可以用BURST TERMINATE命令来产生任意的突发长度。保留状态(Reserved states)主要用于应付未来的不兼容情况而准备的。当一个READ或者WRITE命令被发出之后,突发长度就被选定了。所有的访问操作都会以这个突发长度为限进行读取操作。当突发长度设为2时,A1~A7将会作为数据输入输出的列地址线;当突发长度设定为4时,A2~A7将会作为数据输入输出的列地址线;当突发长度被设定为8时,A3~A7将会作为数据输入输出的列地址线。

(2)突发类型(Burst Type)

突发类型主要分为两种:连续的和交错的,由M3所决定。访问顺序由突发长度、突发类型和起始列地址所决定,如表2。

表2 突发定义

2.2.10 禁止指令和空指令

这两条指令是CS#信号的两个不同的状态。CS#信号可以赋予芯片两种状态:参与工作和休息。CS#处于未激活状态(即禁止指令生效)时,MT48LC4M32B2不对任何传送到这个引脚上的指令作出反应,CS#引脚处于激活状态的情况下才会对传送到引脚上的指令作出反应。

禁止指令(COMMAND INHIBIT)不论CLK信号是否使能,都能阻止新的指令被执行。

空指令(NOP)将激活CS#,可以在电路处于等待或空闲状态时阻止任何不需要的指令被记录。

2.3 MT48LC4M32B2的基本工作过程

2.3.1 MT48LC4M32B2的存储结构

MT48LC4M32B2的内部具有一个存储阵列,类似于表格一样,有行、列之分,当指定一个行地址、一个列地址后,就可以选定一个唯一的存储单元,而整个表格称为逻辑体(Logical Bank,L-BANK)。

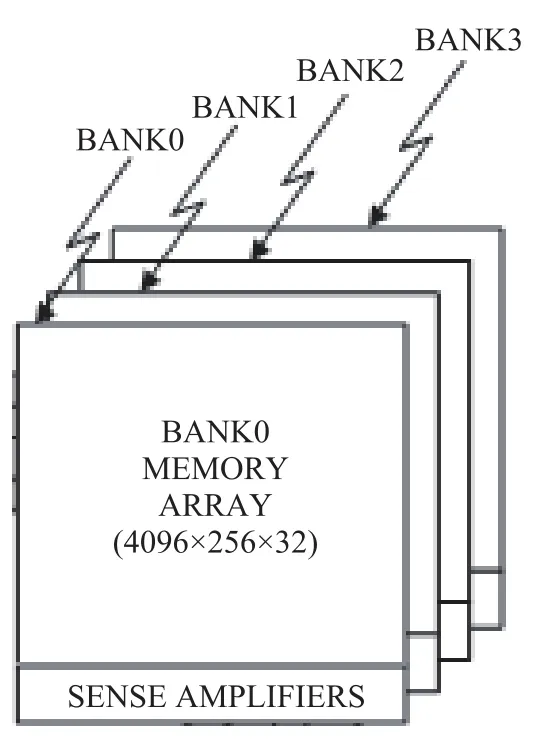

MT48LC4M32B2具有4个L-BANK,每个BANK有4096行,256列,输出数据位宽是32 bit。逻辑结构如图3所示。

图3 MT48LC4M32B2的存储结构

2.3.2 MT48LC4M32B2的工作过程

MT48LC4M32B2的工作电压是3.3 V,且采用同步接口方式(所有的信号都是时钟信号的上升沿触发)。每一个1 M×32 bit bank由4096行×256列个基本存储单元构成,输出数据位宽是32 bit。

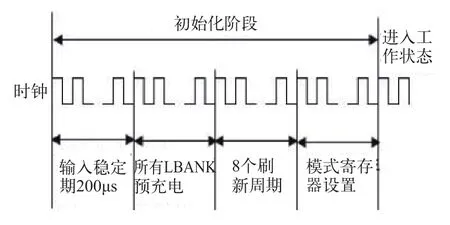

(1)初始化操作

MT48LC4M32B2在上电后必须先对其进行初始化操作,而后才能进行其他操作。初始化具体操作步骤如下:

①上电后需要等待100~200 µs,在等待时间结束后还至少要执行一条空操作命令;

②执行一条预充电命令后,要执行一条空操作命令,这两个操作会使所有存储单元进行一次预充电,从而使存储阵列中的存储单元均处于空闲(idle)状态;

③执行两条自动刷新命令,每一条刷新命令之后,都要执行一条空操作命令,这些操作可以使芯片内部的刷新及计数器进入正常运行状态,以便MT48LC4M32B2为模式寄存器编程做好准备;

④执行加载模式寄存器命令(LOAD MODE REGISTER),完成对MT48LC4M32B2工作模式的设定。

完成以上步骤后,即可进入正常工作状态,以等待外部命令对其进行读、写、预充电和刷新等操作。上述操作过程如图4所示。

图4 初始化步骤

(2)基本读写操作

MT48LC4M32B2的基本读操作需要控制线和地址线相配合,并发出一系列命令来完成,MT48LC4M32B2的读操作只有突发模式(Burst Mode),而写操作则可以有突发写和非突发写两种模式。基本读写过程如下:

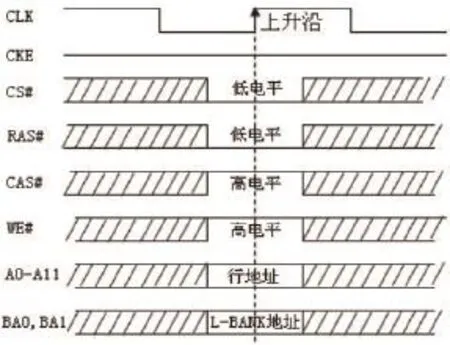

① 行有效

初始化完成后,要想对一个L-BANK中的阵列进行寻址,首先要确定行(row),使之处于激活状态(ACTIVE),然后再确定列。片选和L-BANK的定位是和行有效同时进行的。行有效时序图如图5所示。

图5 行有效时序图

② 列读写

行地址确定之后,即可对列地址进行寻址。在MT48LC4M32B2中,行地址与列地址线是共用的,即A0~A11。读/写命令通过WE#信号的状态来进行区分,当WE#为低电平有效时是写命令,为高电平无效时是读命令。列寻址信号与读写命令是同时发出的。虽然列地址线与行寻址共用,但是CAS(Column Address Strobe,列地址选通脉冲)信号可以区分开行与列寻址的不同。列读写时序如图6所示。

图6 列读写时序图

③ RAS#和CAS#引脚停止激活,等待下一个读写命令。

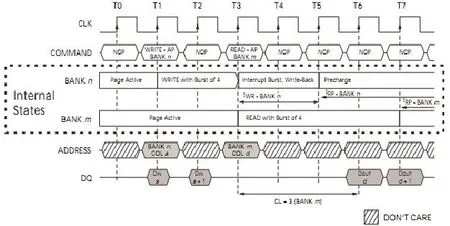

图7所示为一个基本的读写操作时序。

3 MT48LC4M32B2的电特性

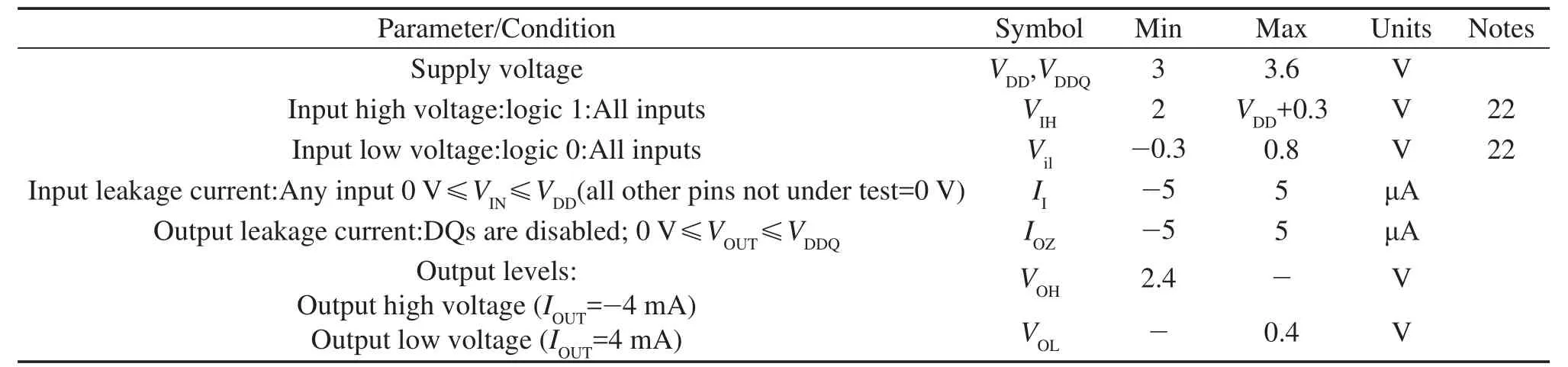

MT48LC4M32B2的部分电特性见表3(VDD=3.3 V ±0.3 V,VDDQ=3.3 V±0.3 V)。

4 MT48LC4M32B2的测试方案

在本案例中,我们选用了Teradyne公司的J750EX测试系统对MT48LC4M32B2进行全面的性能评价。该器件的测试思路为典型的数字电路测试方法,即存储阵列的读写功能测试及各项电特性参数测试。

图7 带有自动预充电的写操作后读出时序

表3 直流电特性

4.1 MT48LC4M32B2的功能测试

针对SDRAM等存储单元阵列的各类故障模型,如阵列中一个或多个单元的一位或多位固定为0或固定为1故障(Stuck at 0 or 1 fault)、阵列中一个或多个单元固定开路故障(Stuck open fault)、状态转换故障(Transition fault)、数据保持故障(Data maintaining fault)、状态耦合故障(Coupling fault)等,有相应的多种算法用于对各种故障类型加以测试,来保证SDRAM等存储系列器件的性能正常,如标准算法MARCH-G,以及其他诸如棋盘格CHECKBOARD、全0、全1、写入恢复(Galloping)、行走(Walking)等算法,本文对此不做深入探讨。

不论何种算法,对于大容量的存储器来说,测试矢量的长度也会随其容量的增加而递增,相应的,测试时间随之增长。以MT48LC4M32B2为例,即使采用较为简单的全0/全1算法,写全页(full page)突发模式,遍历其全部存储单元仍需要约4bank×4096行×256列=4 194 304个以上的周期(还需包括控制指令占用的时间),测试矢量的编写相当繁杂,对此,J750EX测试系统的DSIO模块可以提供一个很好的解决方案。

4.1.1 DSIO简介

DSIO即为Digital Signal Input/Output(数字信号输入/输出)模块的简称,它能使J750EX对数字信号进行发送(source)、抓取(capture)及分析(analyze)等操作。此模块的应用方法十分灵活,转换测试需要输入的高速数字波形,器件寄存器需要动态写入的数字数据,独立存在于数字测试矢量中的数据发送,以及对上述各类数据的抓取操作均可以使用该模块顺利完成。对MT48LC4M32B2的测试就采用了DSIO可以独立于测试矢量,对个别管脚单独发送所需的数字数据这一功能。

4.1.2 采用DSIO模块的测试方案设计

(1)硬件设计

按照DSIO模块所在的测试系统digital board位置,绘制MT48LC4M32B2的测试DUT板,要对器件速率、工作电流、抗干扰等相关因素进行综合考量。

(2)软件设计

考虑到使用该模块为器件提供需要施加激励信号的特殊性,我们采用了J750EX系统的VBT编程模式,在VB环境中调用测试系统资源,来完成相应的控制操作。具体实施步骤如下:

①按照J750EX的标准编程方法,完成对MT48LC4M32B2的PIN脚定义,系统通道定义,PIN LEVELS、TIME SETS、TEST INSTANCE等的设置;

②编写测试矢量,定义A0~A11脚为DSIO的数据source端(digsrc),在pattern中用微控制指令“send”设置数据传送的触发点;

③在测试系统的VB编程环境中调用系统资源,为MT48LC4M32B2施加相应的VDD、VDDQ电压、输入电平等,载入pattern,然后控制DSIO向A0~A11脚发送特定算法生成的数据;

④判别pattern的PASS/FAIL,从而对该项功能测试的正确与否做出判定。

4.2 MT48LC4M32B2的参数测试

MT48LC4M32B2的参数测试方法与通常的数字电路电特性参数测试无甚差别,可完全依照同样的方法进行测试,不再赘述。

5 结束语

对大容量SDRAM的性能进行评价历来就是颇具难度的,不仅要满足高故障覆盖率需求,从而衍生了诸多算法,更要考量如何能简便、有效地开展此类器件的测试评价工作,缩短测试开发周期,降低测试成本。本文以Micron公司的MT48LC4M32B2为例,提出了一种基于Teradyne公司的J750EX测试系统的DSIO模块生成测试矢量的方法,使得大容量(百兆级及以上)SDRAM的功能测试开发更为简便、迅捷,并在此基础上构建SDRAM测试平台,实现大规模生产,以满足SDRAM应用的广泛需求。

[1] Neamen, D A.电子电路分析与设计——模拟电子技术[M]. 清华大学出版社,2009. 118-167.

[2] Synchronous DRAM MT48LC4M32B2-1 Meg×32×4 banks[P]. Micron Technology, In.

The Investigation of the Testing Technology for SDRAM Based on the J750EX Measuring System

WANG Zhengyu, HE Zhiwei, ZHANG Shaoyun

(China Electronics Technology Group Corporation No.58Research Institute,Wuxi214035,China)

The SDRAM(Synchronous Dynamic Random Access Memory) has been widely used for its excellent performance, low price, but due to the fact that the device has a larger capacity (usually a 100 Mb level and above) and the complexity of the implementation for controling, it makes the testing of SDRAM become more difficult, therefore, to explore the SDRAM test technology and create test platform for this kind of the device also has a very important significance. The paper introduces the basic working principle of SDRAM, followed by a detailed describe to the study of the test technology based on J750EX testing system, proposed a method using DSIO resources to achieve the accumulated generating operation of the address for SDRAM. It’s greatly reducing the length of test vectors. It can effectively economize the test time, and reduce the cost of testing. In addition, the key timing parameters of SDRAM, such astRCD(row strobe cycle),CL(read latency),tWR(write back time), can be tested using the test system to send the appropriate control excitations for the device to complete the complicated time cooperate of SDRAM, so that the test requirements of the performance for the device can be achieved.

SDRAM; DSIO; J750EX

TN407

A

1681-1070(2014)08-0018-07

2014-06-11