重离子辐照引发的25 nm NAND Flash存储器数据位翻转

盛江坤,许 鹏,邱孟通,丁李利,罗尹虹,姚志斌,张凤祁,缑石龙,王祖军

(1.西安高技术研究所,陕西 西安 710025;2.强辐射脉冲环境模拟与效应全国重点实验室 西北核技术研究所,陕西 西安 710024)

NAND Flash存储器有着巨大的产量和市场占有率,在笔记本电脑、智能手机、平板电脑等领域应用广泛。由于具有访问速度快、成本低、存储密度大、功耗小、重量轻等特点,NAND Flash存储器非常适合用作卫星系统大数据量存储设备。然而研究[1-2]表明,NAND Flash存储器对辐射环境敏感,给卫星系统可靠运行造成了风险。其中,重离子入射对NAND Flash存储器的影响备受关注。早期的NAND Flash存储器对重离子入射最为敏感的电路是外围电路,而浮栅存储单元由于尺寸较大,即便因为重离子入射发生了电荷损失[3],也未产生较为严重的位翻转。1999年,Nguyen等[4]发现重离子入射导致三星公司的128Mb NAND Flash存储器出现功能中断和由寄存器翻转引发的读出错误,但是未检测到发生在浮栅存储单元的位翻转。随着浮栅存储单元特征尺寸不断缩小,浮栅电荷数量不断减少,位翻转变得更为严重。2006年,Guertin等[5]发现当入射离子LET大于37 (MeV·cm2)/mg时,浮栅电荷损失导致的位翻转随注量累积呈现线性变化,类似于单粒子效应,而入射离子LET小于37 (MeV·cm2)/mg时,位翻转表现为剂量效应。近年来,类单粒子效应的LET阈值已小于1 (MeV·cm2)/mg,甚至低能质子直接电离已足以引起存储单元发生翻转[6-7],因此NAND Flash存储器重离子辐射效应研究一般遵循单粒子效应的研究方法和研究标准,主要关注入射离子特性[8-9]、入射角度[10]、器件工艺尺寸[11-12]以及退火时间[13-15]等因素对位翻转的影响。

一般认为单粒子位翻转截面与注量无关,因此在注量对NAND Flash存储器位翻转的影响方面,当前关注较少[16]。另外,对于重离子入射造成的多单元翻转(multiple-cell upsets, MCU),当前研究更多关注多单元翻转比率及其影响因素,对于多单元翻转的拓扑结构报道较少[9],而拓扑结构信息能够更为直观地反映NAND Flash存储器多单元翻转的特征及其物理机制。为此,本文以两款单层级(single level cell, SLC)NAND Flash存储器为载体开展重离子实验研究,重点关注不同注量下由浮栅电荷损失导致的位翻转特点及其翻转截面的变化,以及多单元翻转拓扑结构特征。

1 实验

1.1 待测器件

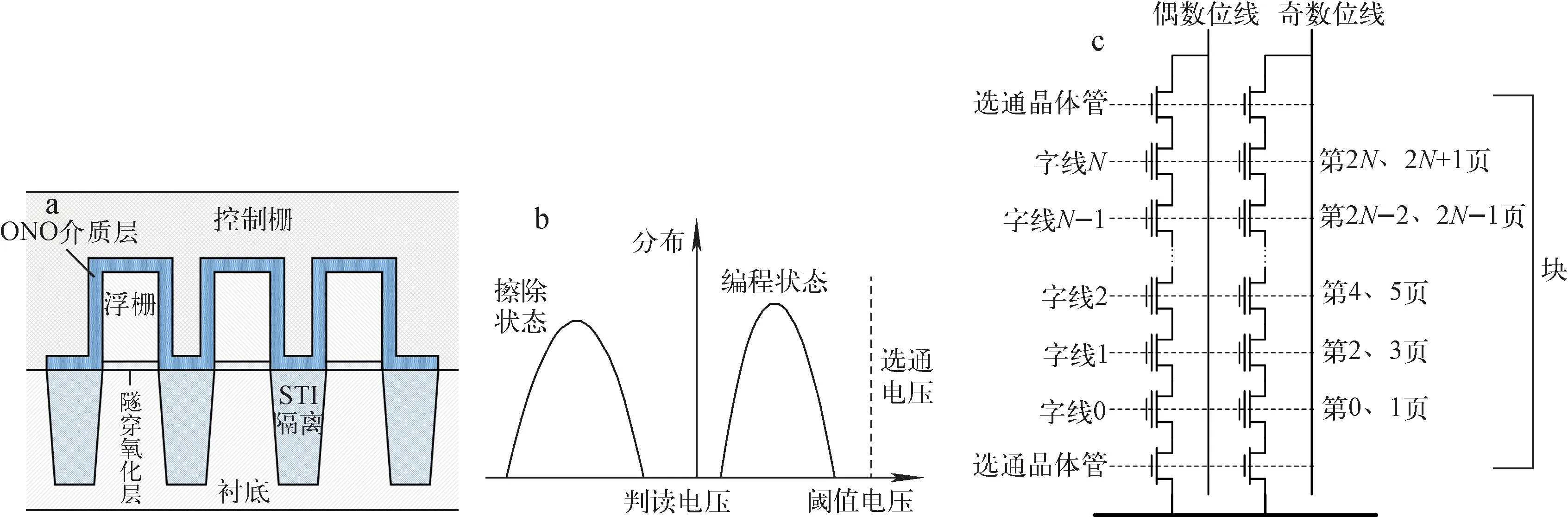

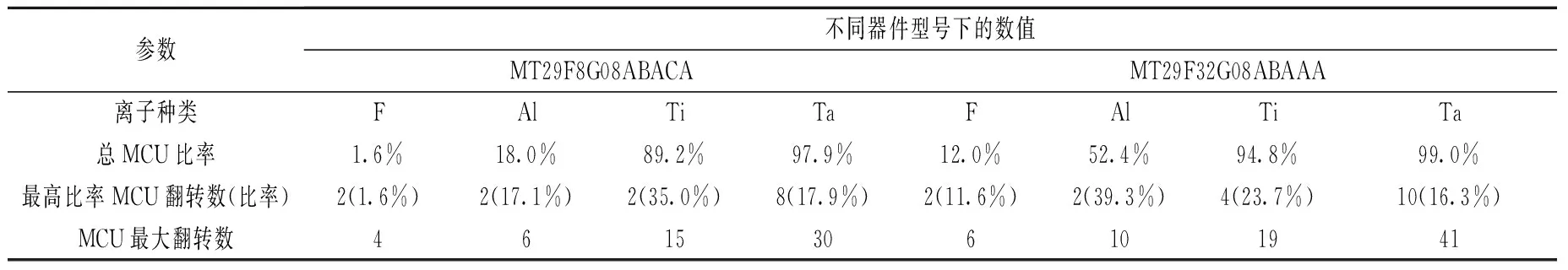

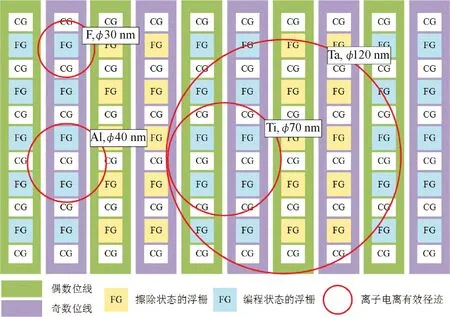

实验选取的两种SLC NAND Flash存储器容量分别为8Gb和32Gb,特征尺寸均为25 nm,供电电压为3.3 V。器件详细参数列于表1。NAND Flash存储单元是浮栅MOS晶体管,其结构如图1a所示,浮栅和衬底之间是隧穿氧化层,浮栅和控制栅之间是由二氧化硅和氮化硅组成的介质层。存储阵列中,多个浮栅存储单元直接串联形成NAND结构。存储阵列阈值电压分布如图1b所示,存储单元逻辑值是由其阈值电压所处的电压窗口决定的。对存储单元进行编程操作后,浮栅中存在过量的电子,存储单元阈值电压升高,存储数据0;执行擦除操作后,浮栅上电子减少,存储单元阈值电压降低,存储数据1。在被访问的存储单元上施加判读电压,并在同一串联结构的其他存储单元和晶体管上施加选通电压,通过串联结构的导通状态来判断存储单元的逻辑值。为避免读出干扰,存储阵列通常设计为位线交错结构,即相邻偶数页和奇数页的存储单元交错排布在一条位线上,如图1c所示。

a——存储单元;b——阈值电压分布;c——存储阵列位线交错设计图1 存储阵列Fig.1 Memory array

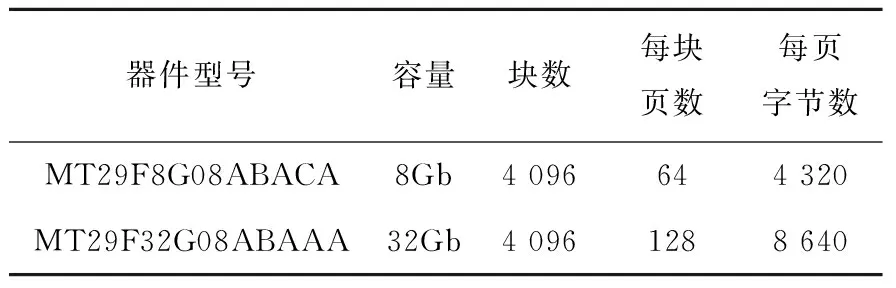

表1 实验器件参数Table 1 Device parameter used in experiment

1.2 实验方案

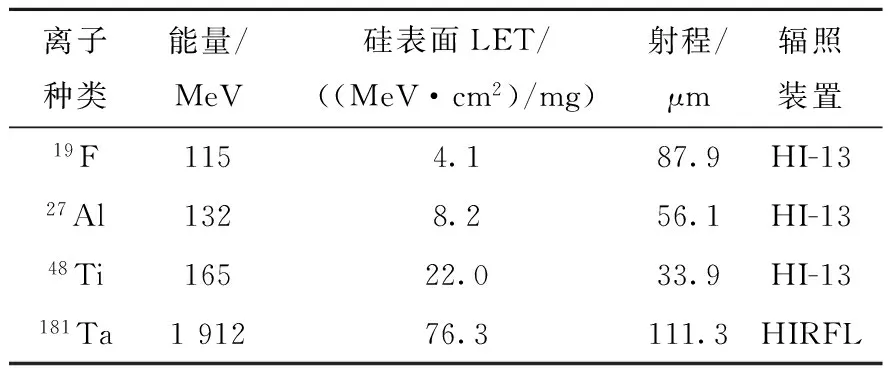

辐照实验在中国原子能科学研究院HI-13串列加速器和中国科学院近代物理研究所兰州重离子加速器HIRFL上开展。室温条件下,以垂直入射方式,采用4种重离子对NAND Flash存储器进行辐照,重离子详细信息列于表2。

表2 重离子信息Table 2 Heavy ions used in experiment

辐照前向被试器件写入数据55 h,辐照过程中被试器件不加电。每累积一定注量时,停止束流输出,为被试器件施加3.3 V电压后,进行位翻转原位测试,记录翻转位地址。测试结束后器件断电并继续辐照。两款器件各随机选取2只进行Ta离子辐照,总注量为4×106cm-2。对于Ti、Al、F离子,每种离子、每种型号各选取4只器件进行辐照,总注量均为1×107cm-2。原位测试由西北核技术研究所开发的R-ictus-Ⅱ型测试系统完成,如图2所示。

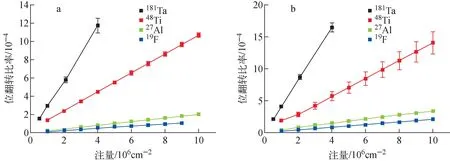

a——MT29F8G08ABACA;b——MT29F32G08ABAAA图3 0到1的位翻转比率随注量的变化关系Fig.3 Bit upset ratio from “0” to “1” as a function of cumulative fluence

2 实验结果与分析

2.1 重离子辐照导致的位翻转

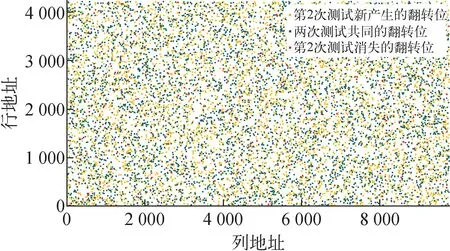

辐照过程中仅检测到0到1的位翻转,未检测到1到0的位翻转。位翻转比率与注量基本呈线性关系,如图3所示。位翻转具有随机性、继承性、少量短时退火以及可再次编程等特点。翻转位在地址上呈随机分布,前一次检测到的翻转位绝大部分可在当次测试中检测到,仅少量翻转位消失。翻转位仍能通过擦除和编程操作再次存储数据1或0。图4为Ti离子注量从5×106cm-2增加到1×107cm-2时,32Gb器件新增、消失以及共同拥有的翻转位。重离子注量为1×107cm-2时,两款器件翻转位消失数约是注量为5×106cm-2时检测到的翻转数的3%。

Ti离子注量分别为5×106 cm-2、1×107 cm-2图4 32Gb器件翻转位对比Fig.4 Comparison of bit upset for 32Gb device

位翻转特点表明位翻转是由浮栅电荷损失造成的。重离子入射导致浮栅电荷损失的机制有两种,一是载流子通过氧化层势垒流出浮栅的净通量[17]。浮栅、控制栅以及衬底产生的电子空穴的高能部分会形成越过氧化层势垒进出浮栅的通量。器件未加电时,编程状态下,浮栅中的过量电子会在氧化层形成指向浮栅的电场。在电场的作用下,浮栅电子的流出通量大于流入通量,空穴流入通量大于流出通量,净通量导致浮栅中的电子减少。二是氧化层中电子空穴对的产生、复合和传输[18]。重离子在浮栅周围的氧化层中形成电子空穴对。在氧化层电场作用下,电子迅速漂移至衬底,一部分空穴形成氧化物陷阱电荷,屏蔽浮栅负电荷,另一部分进入浮栅中进一步导致浮栅电荷减少。当氧化物陷阱电荷退火后,屏蔽作用减弱,使得少量位翻转消失。入射离子LET越大,在浮栅及其周围沉积能量越多,浮栅电荷损失越严重,相同注量下翻转比率也就越高。

对于重离子入射事件,存储单元被击中次数的概率可通过泊松分布表示为:

(1)

其中:P(k)为在1个间隔中存储单元被击中k次的概率;λ为在1个间隔中存储单元被击中的平均次数。实验中离子最大注量为1×107cm-2,而25 nm NAND Flash存储密度约在1010cm-2量级,即便考虑下一小节讨论的多单元翻转,λ仍是一个远小于1的数值,从而有:

(2)

式(2)表明实验中存储单元被击中两次以上的概率很小,被击中的存储单元绝大多数仅被击中1次,因此位翻转比率与注量呈现较好的线性关系。可以推测,当重粒子注量与存储密度可比时,存储单元被多次击中的概率升高,翻转率斜率将会降低。但不同于已翻转的SRAM存储单元再次被击中后可能再次翻转的情况,浮栅存储单元被多次击中时只会使浮栅电荷损失更多,因此,随着注量的累积,SRAM和NAND Flash存储器翻转率斜率的降低程度可能不同。

虽然8Gb器件和32Gb器件都采用25 nm工艺,但图3显示,相同注量下8Gb器件位翻转率小于32Gb器件。由于两款器件在设计上存在差异,如8Gb器件的存储密度和32Gb器件相近但浮栅尺寸要略大于32Gb器件、存储阵列的块页容量不同、负载差异导致编程后浮栅电荷数量不同等方面,使得两款器件的位翻转率虽然有着相同的变化趋势,但是数值并不一致。

2.2 多单元翻转

由于位翻转比率和注量之间存在线性关系,可定义存储阵列的单粒子位翻转截面和单粒子翻转事件截面。单粒子位翻转截面表示为:

(3)

其中:n为翻转数;N为被检测的存储单元数量;Φ为离子注量,cm-2。单粒子翻转事件截面表示为:

(4)

其中,nEvent为翻转事件总数,有:

(5)

其中,ni-Event为翻转数为i的单粒子翻转事件数量,当i=1时,n1-Event表示单单元翻转(single-cell upset, SCU)事件数量,当i>1时,ni-Event表示多单元翻转事件数量。根据各参数定义,有:

(6)

多单元翻转比率反映了多单元翻转事件的严重程度,可为NAND Flash存储器抗辐射加固设计以及系统抗辐射加固方案提供重要参考。定义多单元翻转比率:

(7)

ηi也可理解为1个存储单元因为翻转数为i的单粒子翻转事件而翻转的概率。σSEU/σE-SEU可理解为单粒子翻转事件中翻转位数的平均值,即:

(8)

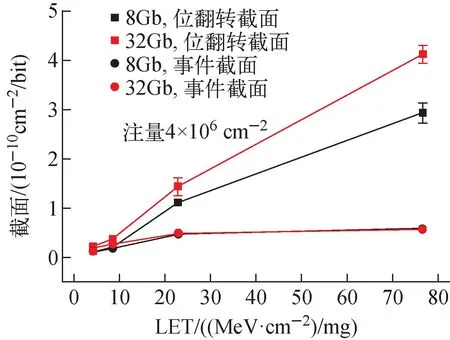

图5 8Gb器件和32Gb器件的翻转截面Fig.5 Cross sections for 8Gb device and 32Gb device

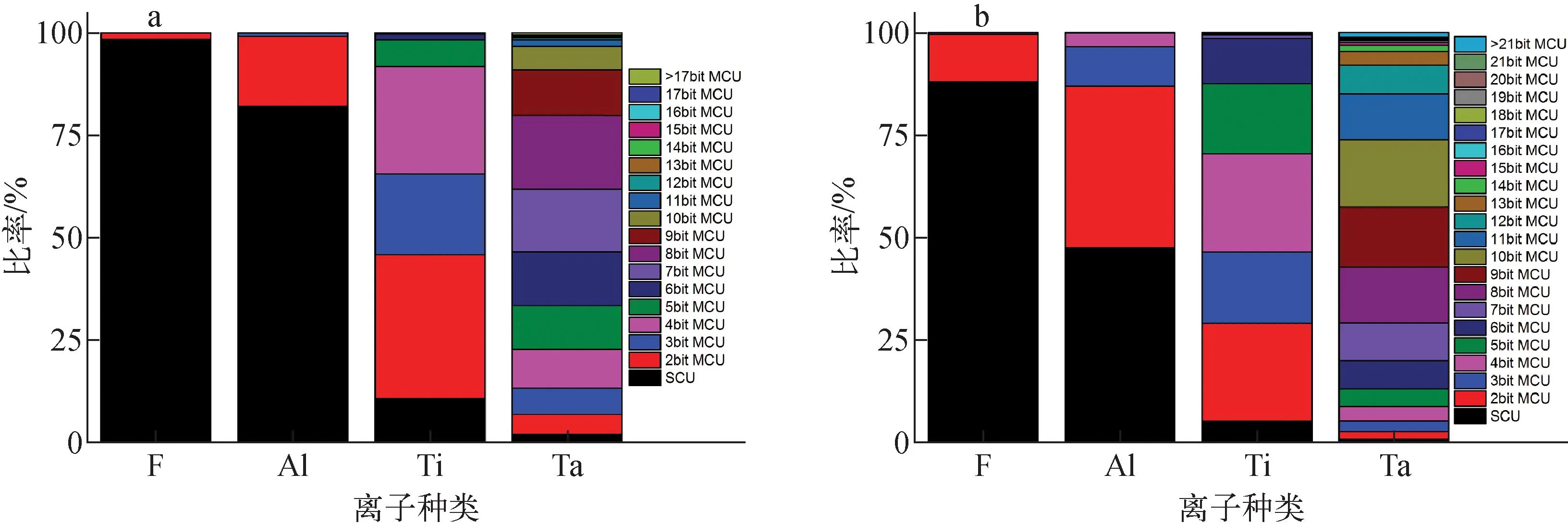

图6为离子注量为4×106cm-2时,8Gb器件和32Gb器件的多单元翻转比率。表3列出了多单元翻转统计信息。从图6、表3可看出,随着入射离子LET的增加,总的多单元翻转比率不断增大,多单元翻转比率最大值出现在翻转数更多的多单元翻转事件上,单粒子翻转事件所能包含的最大翻转数也被不断突破。

a——MT29F8G08ABACA;b——MT29F32G08ABAAA图6 不同入射离子辐照时多单元翻转比率Fig.6 MCU ratios for different heavy ions

表3 多单元翻转统计信息Table 3 Statistical information of MCU

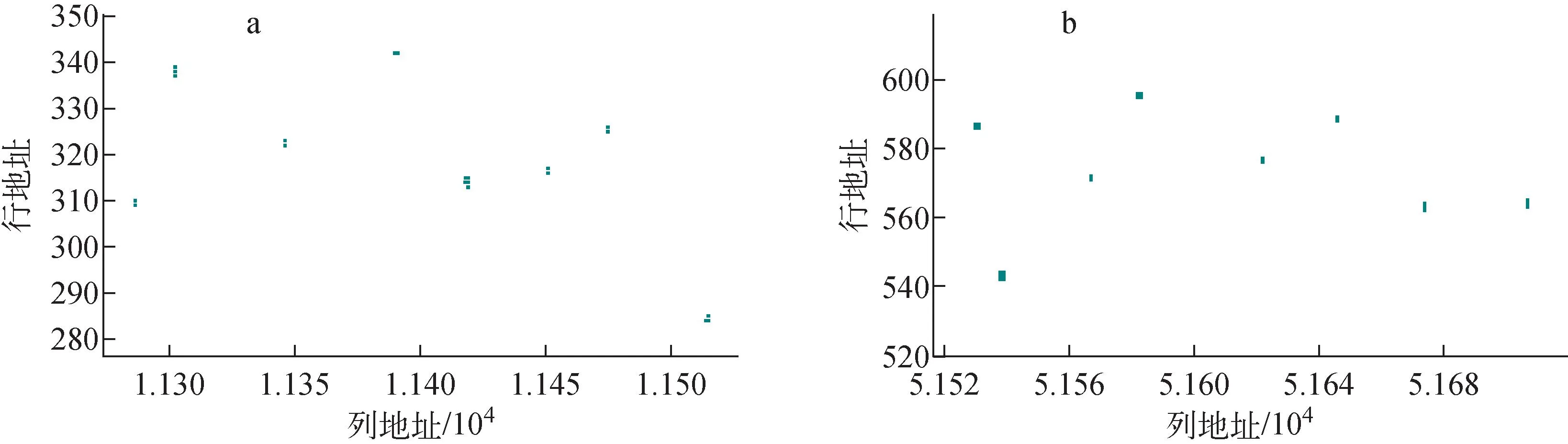

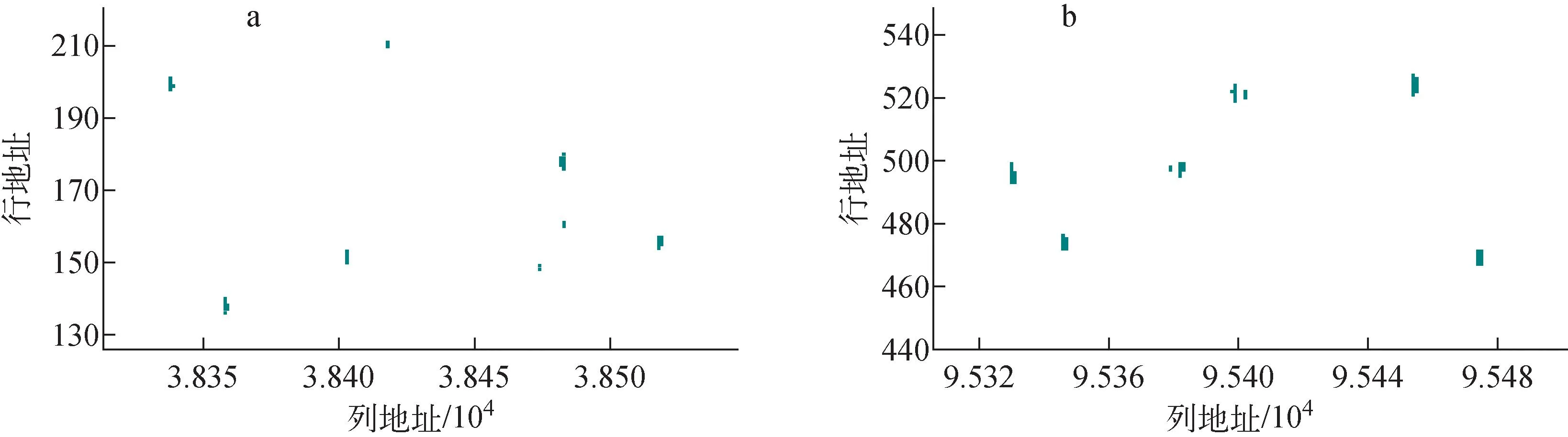

图7、8分别为Ti离子和Ta离子入射时,两款器件部分地址的多单元翻转位图。Ti离子造成的多单元翻转拓扑结构基本上呈单列或双列形式,极少数是行形式,这可能是因为位线间的存储单元通过STI进行隔离,而同一位线的存储单元是源漏共用的串联结构,具有更高的电荷共享效率[1]。Ta离子入射时,多单元翻转拓扑结构基本上呈双列形式,少量是列间隔形式。

a——MT29F8G08ABACA;b——MT29F32G08ABAAA图7 Ti离子注量1×107 cm-2时8Gb器件和32Gb器件的多单元翻转位图Fig.7 MCU maps for 8Gb device and 32Gb device at Ti cumulative fluence of 1×107 cm-2

a——MT29F8G08ABACA;b——MT29F32G08ABAAA图8 Ta离子注量4×106 cm-2时8Gb器件和32Gb器件的多单元翻转位图Fig.8 MCU maps for 8Gb device and 32Gb device at Ta cumulative fluence of 4×106 cm-2

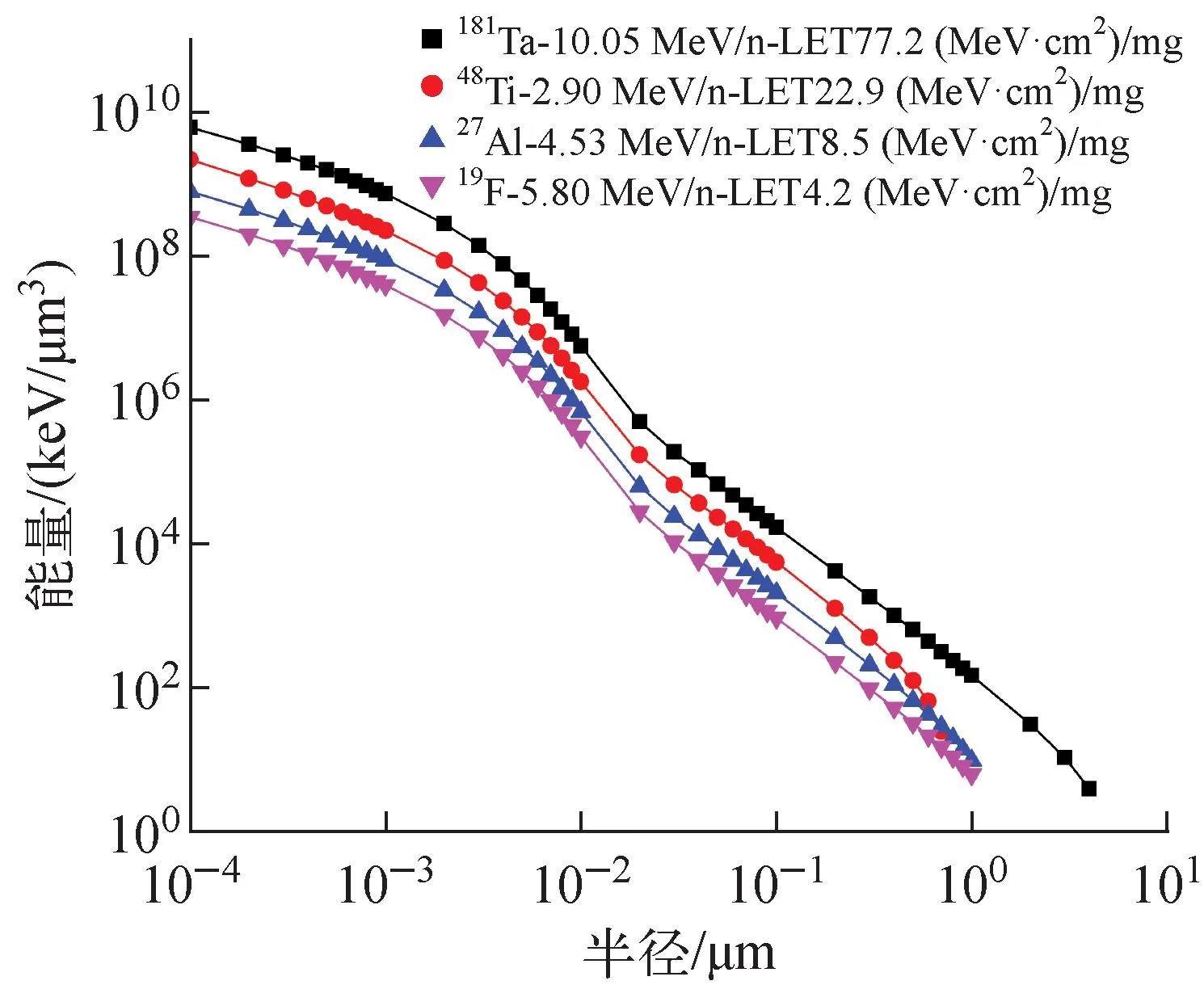

对于多单元翻转的讨论可以从离子电离径迹入手。Fageehea等[19]发展了离子电离径迹的解析模型。利用TRIM程序计算了重离子通过介质层和金属布线层到达浮栅时的能量和LET,代入Fageehea等的解析模型,计算了离子能量沉积密度径向分布,如图9所示。可发现,不同离子相同位置处的能量沉积密度随LET的增大而增大;单核子能量越高,转移到σ电子的能量越大,离子电离径迹半径越大。实验结果表明,多单元翻转比率与离子LET呈正相关,表明多单元翻转的主要影响因素是能量沉积密度,离子电离径迹边缘处已不足以造成位翻转。当1个离子在一定范围内沉积的能量足以引起多个存储单元产生严重的浮栅电荷损失时,会造成1个多单元翻转事件。

图9 不同重离子的能量沉积径向分布Fig.9 Radial distribution of energy deposition for different heavy ions

NAND Flash存储阵列采用了位线交错设计,但由于存储密度很大,难以像SRAM一样采用位交错设计,因此当存储数据为55 h时,从物理地址来看,1个块内每两列串联结构交替存储数据0和数据1,如图10所示。定义重离子电离有效径迹半径为重离子入射造成的比率最大的多单元翻转事件尺寸。以32Gb器件为例,Ta离子入射造成的比率最大多单元翻转是10 bit,以双列形式定性估计Ta离子电离有效径迹半径约为120 nm。根据图9中Ta离子位于120 nm处的能量沉积密度反推Ti、Al、F离子的电离有效径迹半径分别约为70、40、30 nm,如图10所示。由于浮栅存储单元具有非易失性,不加电条件下仍能处于编程或擦除状态。对Ta离子来说,如果径迹中心位于初始状态为编程状态的存储单元附近,将会引发双列形式的多单元翻转事件,如果径迹中心位于初始状态为擦除状态的存储单元附近,由于擦除状态的存储单元难以发生翻转,将产生列间隔形式的多单元翻转事件。对F、Al、Ti离子来说,其电离有效径迹分别能覆盖1~2、2~4、4~6个存储单元。这一定性的分析结论既与实验得到的位翻转截面一致,也与多单元翻转统计结果相一致。另外,从列间隔形式的多单元翻转事件可推测,在空间应用中,当入射离子LET足够高,或者1个字节内的相邻位均为编程状态时,重离子入射可能会造成同一字节多位翻转,对数据纠错带来更大挑战。

图10 32Gb器件存储阵列上的数据存储与重离子电离有效径迹示意图Fig.10 Data stored in 32Gb memory array and effective ion track

2.3 注量对位翻转的影响

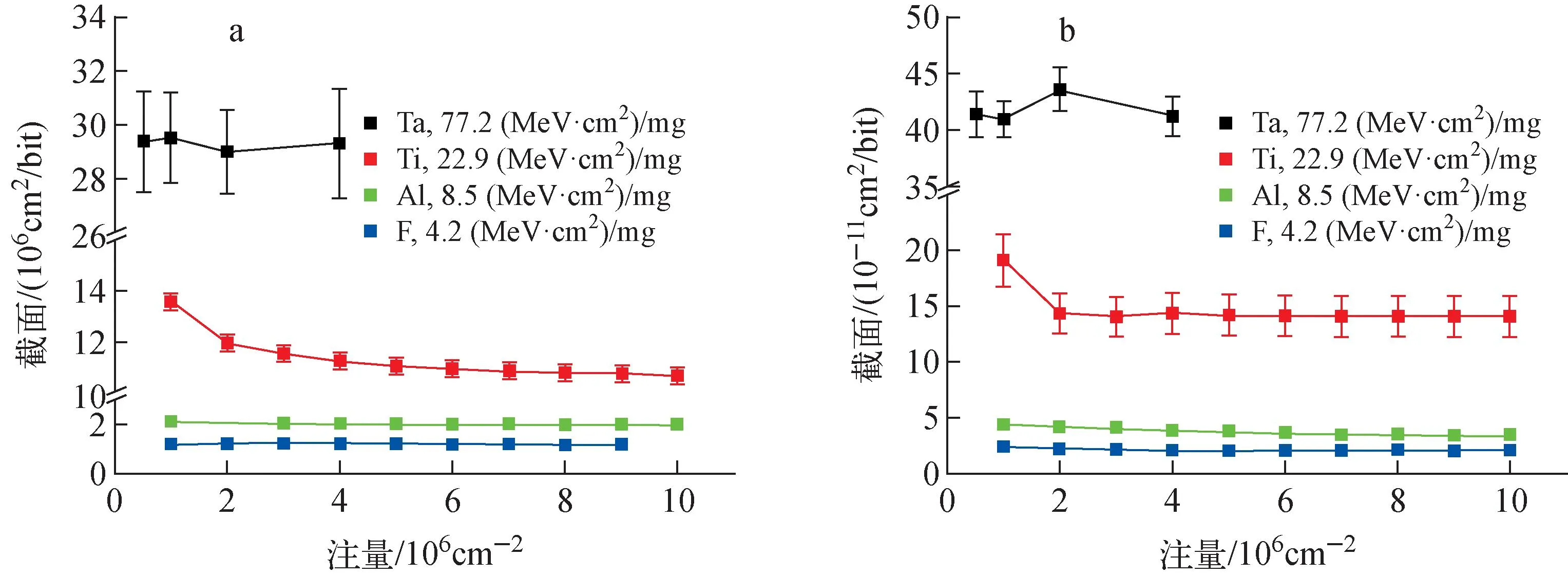

图11为根据式(3)计算得到的4种离子在不同注量下的位翻转截面。虽然实验检测到的位翻转比率与注量呈现较好的线性关系,但是随着注量累积,F、Al、Ti离子对应的位翻转截面呈现降低趋势,其中Ti离子对应的位翻转截面变化最为明显。

a——MT29F8G08ABACA;b——MT29F32G08ABAAA图11 不同注量下的位翻转截面Fig.11 Bit upset cross section as a function of cumulative fluence

从γ射线辐照结果来看,存储单元的阈值电压并非随机分布在存储阵列上,处于编程状态阈值电压分布低压区的存储单元倾向于在相邻或靠近的地址上集中分布,在辐射环境下更容易发生翻转[20-21]。图12为不同Ti离子注量下,32Gb器件存储阵列某块在行地址上的位翻转密度。从图12可看出,辐照初期,翻转的存储单元更多处于某些集中的地址。这类存储单元翻转截面较大,但是数量较少。随着注量累积,由于这类存储单元数量迅速减少,在所有位翻转中占比越来越小,而其他大量存储单元的翻转数增长率变化不明显,因此分布开始变得更加均匀,从而整体上呈现出位翻转截面降低的趋势。

图12 Ti离子辐照下32G器件第200块的位翻转分布Fig.12 Bit upset distribution of the 200th block of 32Gb device under Ti irradiation

这一现象可通过一个简化的数学模型来解释。假设更容易发生翻转的存储单元的数量是N1,其翻转截面为σ1,其他存储单元的数量为N2,翻转截面为σ2,N1≪N2,σ1≫σ2,有:

N=N1+N2

(9)

仅考虑存储单元被击中1次的情况,根据泊松分布,有:

(10)

当入射离子LET很小,如Al、F离子,σ1很小,σ2约为0,有:

(11)

表明位翻转截面随注量累积缓慢变小。当入射离子LET很大,如Ta离子,σ2不再是0,此时N1σ1≪N2σ2,e-Φσ1 (12) 因此统计涨落、测量误差等因素会造成截面变化不明显甚至波动。当入射离子LET处于中间值,如Ti离子,N1σ1和N2σ2在量级上可比,即有: (13) 此时σ1要大于入射离子LET很小时的σ1,因此相同注量下Ti离子对应的σSEU的变化相比于F、Al离子对应的σSEU更为明显。 为了研究不同注量下NAND Flash存储器位翻转特点及其翻转截面的变化,以及重离子入射导致的多单元翻转,以两款25 nm SLC NAND Flash存储器为载体开展了重离子实验研究。 实验发现重离子入射导致的位翻转具有随机性、继承性、少量短时退火以及可再次编程等特点,表明位翻转主要是由存储单元浮栅电荷损失造成。25 nm工艺节点下的浮栅存储单元对于重离子入射敏感,1个重离子在击中灵敏体积的情况下足以引起位翻转,因此当注量远小于存储阵列密度时,位翻转比率随注量累积基本呈线性变化。 重离子导致两款器件出现多单元翻转。多单元翻转的严重程度与入射离子LET正相关,其存在导致单粒子位翻转截面并未达到饱和,这意味着基于威布尔拟合的单粒子位翻转截面评估方法可能难以适用于NAND Flash存储器,或者可能存在较大误差。由于存储阵列采用了位线交错设计,当存储向量为55 h时,多单元翻转拓扑结构呈现单列、双列以及列间隔形式。利用离子电离径迹模型估算得到离子电离有效径迹半径,半径估计值与实验得到的位翻转截面和多单元翻转统计结果一致。可推测,在空间应用中,当入射离子LET足够高,或者1个字节内相邻位均处于编程状态时,重离子入射会造成同一字节多位翻转,对数据纠错带来更大挑战。 随着注量累积,两款器件的位翻转截面存在下降趋势,这是由于处于编程状态阈值电压分布低压区的存储单元倾向于在相邻或靠近的地址上集中分布,随着注量累积,这类存储单元数量迅速减少,而其他大量存储单元的翻转数增长率变化不明显。这一现象在Ti离子入射时尤为显著。位翻转截面与注量的关系意味着较高注量下得到的位翻转截面可能会低估NAND Flash存储器在轨翻转率,利用较低注量获取位翻转截面可能会更为保守或者准确地评估NAND Flash存储器在轨翻转率。3 结论