一种新型高抗辐照可配置SOI器件技术

叶甜春,李 博,刘凡宇,李多力,李彬鸿,陈思远

(1.中国科学院 微电子研究所,北京 100029;2.中国科学院大学,北京 100049;3.中国科学院 硅器件技术重点实验室,北京 100029)

随着“问天”火星探测器、“嫦娥”系列月球探测器、载人空间站等任务的成功实施,我国正由航天大国向航天强国迈进。根据国家航天局发布的相关计划,未来10~15年,我国将开展火星采样、小行星采样、木星、天王星等行星探测,后续还将前往太阳系边缘进行科学探测。另一方面,随着我国“双碳战略”的实施,核电站建设加快部署。根据《“十四五”现代能源体系规划》,“在确保安全的前提下,积极有序推动沿海核电项目建设,合理布局新增沿海核电项目;到2025年,核电运行装机容量将达到7 000万千瓦左右,使我跻身世界核电大国之列”。

航天和核能装备的核心是抗辐照器件。工作在空间和核辐射环境中的微电子器件受种类不同、能量不一的粒子和光子照射,将导致性能退化甚至功能失效。电离辐射效应主要包括:总剂量效应(total ionizing dose effect, TID)[1-3]和单粒子效应(single event effect, SEE)[4-5]。总剂量辐射效应为入射粒子或光子在器件二氧化硅中产生电子-空穴对,电子-空穴对的分离、输运形成氧化物陷阱电荷和界面陷阱电荷等缺陷,导致器件的电参数发生改变。单粒子效应多出现在半导体器件的PN结区域,产生的电子-空穴对被PN结收集形成脉冲信号,可能导致芯片出现数据错误,甚至无法正常工作。

绝缘体上硅(silicon-on-insulator, SOI)晶体管由于埋层氧化物(buried oxide, BOX)隔离,天然对闩锁免疫。此外,SOI硅膜厚度较薄,因而相比体硅器件,单粒子敏感度更低。SOI器件特有的闩锁免疫和单粒子低敏感度,使其广泛应用于空间和核工业等领域。然而,BOX层的存在使SOI器件受总剂量效应影响比较严重,导致器件性能退化,甚至失效。美国政府重点支持了Skywater、Honeywell、Harris和Atmel四家公司发展抗辐照SOI技术,抗总剂量辐照水平达到1 Mrad(Si)以上、单粒子软错误小于10-11错误/(位·天)(地球同步轨道100 mil铝屏蔽后方单粒子辐射环境)。对于微电子器件,传统的抗辐照加固方法主要包括工艺加固、版图加固和电路设计加固。工艺加固通过注氧离子、氮离子等引入缺陷能级捕获辐射引入的空穴[6-7],但引入的缺陷能级可能对器件的可靠性造成影响。版图加固通过规定版图形状(环形栅、H型栅等)[8-9]、加宽特定敏感单元间距[10]等方式减少辐照对器件的影响,但该方法增加了版图面积开销。电路设计加固方法有三模冗余[11]、双互锁存单元(dual interlocked storage cell, DICE)[12]等,但该方法不仅增加了芯片面积,还降低了电路性能。面对深空探测和核应急等更加复杂恶劣的场景,以上方法均难以确保集成电路在强辐照环境下仍保持良好的性能[13]。近来,SOI器件背栅调控辐照效应受到关注[14],为提高电路抗辐照能力提供了新思路。该方法通过在背栅施加电压抑制或补偿总剂量引起的氧化物陷阱电荷的产生,同时阻断有源区单粒子产生的离化电荷输运,简单易于实现。然而SOI器件衬底的PN结隔离限制了背栅调控粒度和范围,难以实现晶体管级粒度的大电压范围调控,可能造成补偿不足或过补偿现象,从而降低电路的抗辐照水平。

中国科学院微电子研究所提出的可配置(configurable SOI, CSOI)技术不仅继承了SOI器件低单粒子敏感度和闩锁免疫能力,而且增加配置层还可以调控顶层晶体管的寄生晶体管效应。因此,CSOI结构能提高电路敏感单元的抗单粒子能力。在总剂量效应方面,CSOI器件的绝缘层是主要诱因。通过对CSOI器件的配置层施加相应的偏置电压,不仅抑制了背栅晶体管的开启,而且补偿了绝缘层辐照诱生陷阱电荷对前栅晶体管的影响。此外,不同于全耗尽SOI结构单一的背栅调控机制,CSOI器件独立的背栅调控特性可提高电路抗辐照加固设计的灵活性。本文介绍CSOI结构与制备工艺,分别阐释CSOI器件与电路总剂量和单粒子效应,并给出配置层偏置策略。

1 CSOI结构与制备工艺

1.1 结构特点

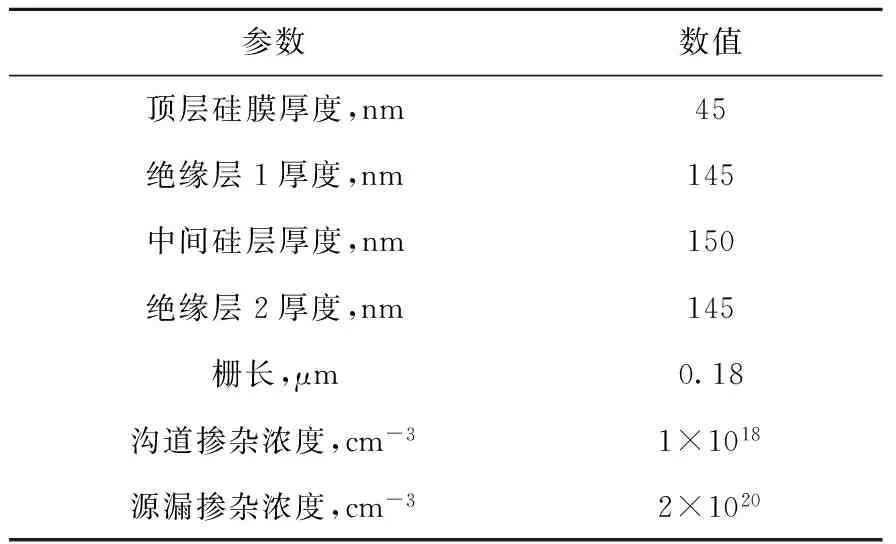

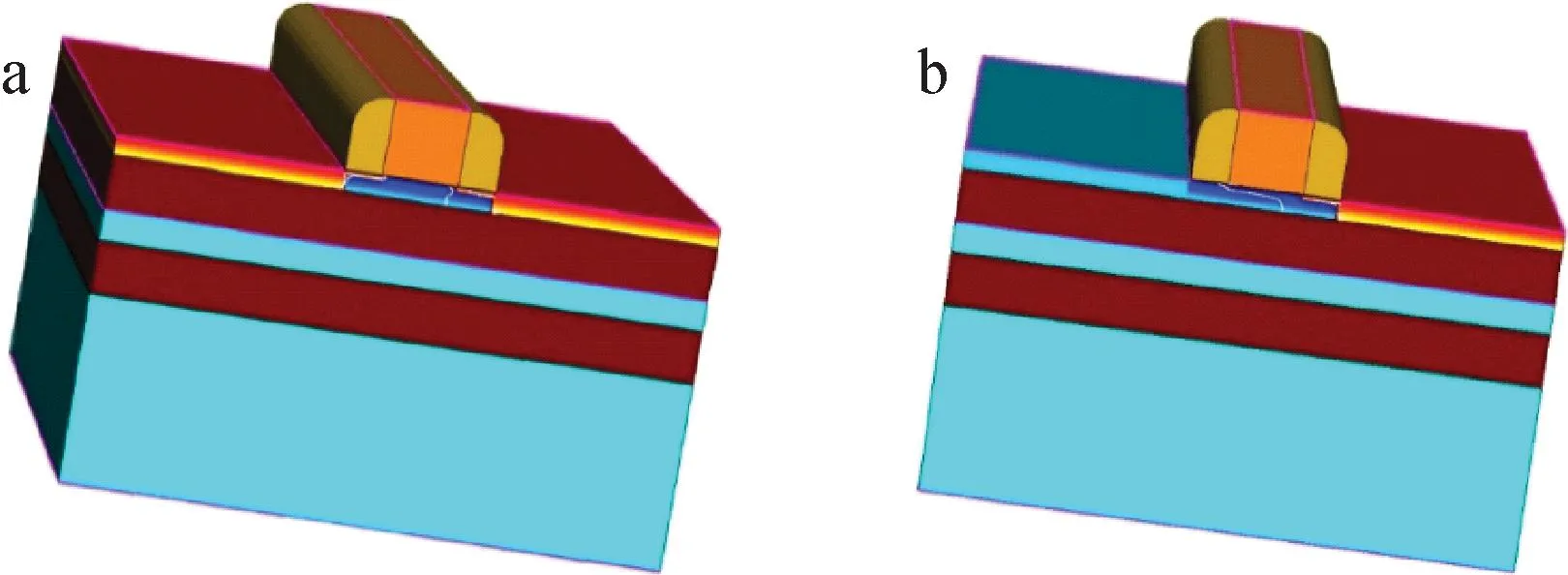

CSOI器件由自上而下的功能层、绝缘层1、配置层、绝缘层2和衬底5层结构组成,如图1所示。其中,功能层用于器件制备;绝缘层1和2分别为第1层和第2层埋氧层(即BOX1和BOX2);配置层位于绝缘层1和2之间,为N型或P型硅,可实现对功能层器件性能的调控;衬底起到机械支撑作用。CSOI晶圆可采用两次层转移,并结合晶圆级键合技术实现。CSOI器件结构和工艺关键信息列于表1。为了提高功能层器件的调控能力,同时减小单粒子敏感体积,顶层硅膜厚度设定为45 nm。BOX1和BOX2的厚度均为145 nm,配置层厚度为150 nm。CSOI器件最小沟道长度为0.18 μm,沟道掺杂浓度约为1018cm-3,源漏掺杂浓度为2×1020cm-3,配置层可掺杂为N型或P型,掺杂浓度为5×1017cm-3。与传统SOI器件相比,CSOI器件有以下特点:1) 配置层作为器件的背栅,实现器件性能的调控;2) 配置层全隔离,使器件背偏电压调控幅度增加、粒度缩至晶体管级;3) BOX2屏蔽了衬底的影响。

表1 CSOI器件的工艺参数Table 1 Process parameter of CSOI device

图1 CSOI MOS器件结构示意图(a)和TEM图(b)Fig.1 Structure schematic diagram (a) and TEM diagram (b) of CSOI MOS devices

1.2 工艺制备流程

中国科学院微电子研究所基于国产0.18 μmCMOS平台成功开发出抗辐照CSOI工艺。CSOI特有工艺主要包括配置层的隔离、掺杂和引出等工艺步骤。首先,在有源区隔离部分,除了对功能层进行浅槽隔离(STI)外,还增加了配置层的浅槽隔离。其次,为了减小背偏电压在中间硅层的能量耗散,采用离子注入的方式对配置层进行了掺杂。最后,配置层的引出工艺为先刻蚀出BOX1层窗口,接着制备硅化物,最终完成介质填充、接触孔和金属的制备。

2 CSOI总剂量效应及加固

对于本文所提出的新型CSOI结构,栅氧化层很薄(2.9 nm),其辐照感生的电荷可忽略不计[15]。因此,辐照引起器件失效的主要原因来自于BOX1、BOX2和STI。由于总剂量辐照后NMOS器件的性能退化严重,因此本节将基于CSOI NMOS条型栅器件,研究不同氧化层辐照感生电荷对器件性能的影响机制,以及背偏电压对器件总剂量效应的调控机理,并通过CSOI 4kb SRAM的60Co γ射线辐照实验验证其抗总剂量水平。

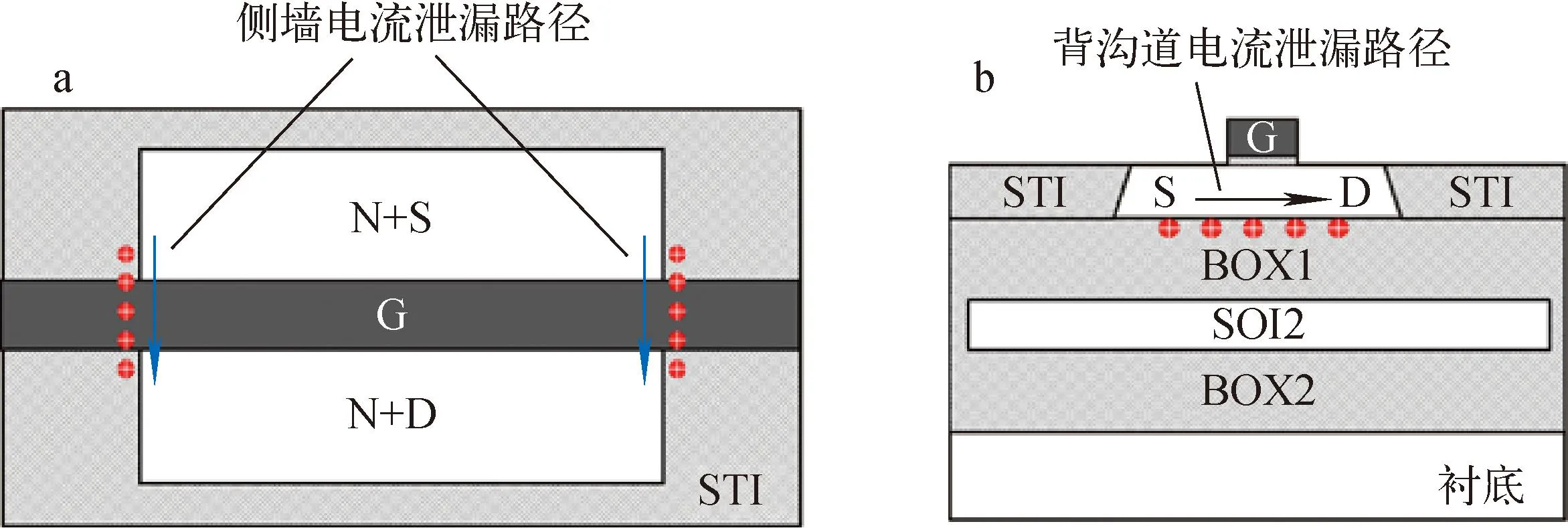

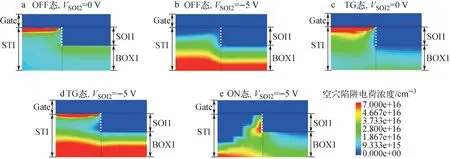

总剂量辐照后,氧化层中的辐照感生陷阱电荷会导致NMOS晶体管中的P型体区耗尽甚至反型,形成寄生导电沟道。如图2所示,在CSOI NMOS条栅晶体管中存在两种漏电路径:1) 由STI中空穴陷阱电荷引起的从源到漏的侧墙漏电路径;2) 由BOX层中空穴陷阱电荷引起的背沟道漏电路径。这些漏电路径会导致器件关态漏电流增加,从而影响集成电路的整体静态功耗。

图2 CSOI结构中两种总剂量辐照引起的电流泄漏路径Fig.2 Two current leakage paths caused by total dose irradiation in CSOI structure

CSOI晶体管总剂量辐照响应对辐照中前栅晶体管的偏置状态有很强的依赖性。图3为5种辐照偏置状态下CSOI NMOS器件辐照前后的转移特性曲线。总剂量辐照用北京大学60Co辐照源进行,测试过程中所有器件的背栅偏置电压均为0 V。从图3可看出,随着辐照剂量的增加,晶体管转移特性曲线向左漂移加剧,且漏电流急剧增加。其中,以OFF态和ON态偏置条件下的器件性能退化最为明显,但这两种偏置状态下的漏电机制却不尽相同。OFF态偏置下,器件漏电流主要来自于BOX1中空穴陷阱电荷引起的背沟道反型。而ON态偏置下,器件漏电流主要来自于STI中俘获的大量空穴电荷导致的侧边漏电,其最明显的表现为图3e中亚阈值区域出现的“驼峰效应”(hump effect)[16]。

辐照过程中,通过图3a、b对比与图3c、d对比,发现对CSOI器件施加负的背栅偏置电压,可有效抑制由总剂量效应引起的背沟道漏电。这可以归因于辐照过程中,由负的背栅偏置电压施加在BOX1层上的额外电场。该电场影响了BOX1层中的电荷产生率、空穴俘获率和空穴陷阱电荷分布。在负背栅偏置电压所产生的垂直电场的作用下,空穴陷阱电荷主要分布在BOX1层底部,减弱了其对前栅晶体管电学性能的影响。而对于侧墙漏电,这种加固方法并未展现出很好的抑制效果,如图3e所示。

测试过程中,对CSOI器件施加负的背栅偏置电压,可有效减弱总剂量辐照响应对辐照中前栅晶体管偏置状态的依赖性。图4为背栅电压为-5 V偏置下CSOI NMOS器件5种偏置状态辐照前后的转移特性曲线。从图4可看出,对于所有辐照偏置状态,测试过程中施加负的背栅偏置电压可显著抑制晶体管的泄漏电流,降低阈值电压漂移量,展现了良好的总剂量抑制效果。当辐照剂量累积到2 Mrad(Si)时,对于OFF态VSOI2=0 V辐照偏置下的晶体管,其泄漏电流在10-11A量级。而对于剩余的其他4种辐照偏置状态,其泄漏电流均在10-12A量级。这主要归功于负的背栅偏置电压施加在BOX1层上的额外电场,由BOX1和STI中空穴陷阱电荷引起的电场线更多终止在负的SOI2层,而不是有源区中的自由载流子。这样就阻止了有源区反型层的产生,从而有效抑制了辐照引起的泄漏电流。

Ldd为轻掺杂漏结构图5 BOX2层不同空穴陷阱电荷密度下CSOI器件背沟道处的电场分布Fig.5 Electric field distribution at back channel of CSOI device under various hole trapped charge densities

为进一步研究不同氧化层辐照感生电荷对器件性能的影响机制,以及辐照过程中负背偏电压对氧化层中陷阱电荷分布的调控机制,本文利用Sentaurus TCAD仿真软件建立了CSOI NMOS二维/三维仿真模型,并基于该模型进行总剂量效应仿真。

2.1 BOX2层辐照感生电荷对器件性能的影响机制

仿真过程中,背栅偏置电压设置为0 V,BOX1层中空穴陷阱电荷密度为0 cm-2,BOX2层中空穴陷阱电荷密度分别为0 cm-2(辐照前)和1×1017cm-2(辐照后)。仿真得到的CSOI晶体管背沟道电场分布如图5所示。从图5可看出,由于SOI2层0 V电压的屏蔽作用,BOX2层中的空穴陷阱电荷对功能层电场的影响很小。仿真所得到的辐照前后前栅晶体管阈值电压漂移量仅为2.8%。因此,CSOI器件总剂量效应引起的性能退化主要来自于BOX1层和STI中的辐照感生电荷。

2.2 STI中陷阱电荷非均匀分布的影响机制

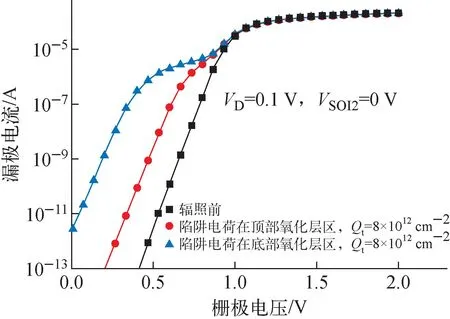

为进一步了解STI中电荷分布的影响机制,本文在仿真中引入了非均匀电荷分布模型。如图6所示,STI中与SOI1层平行的部分被分为两个区域:顶部氧化层区(从0~25 nm)和底部氧化层区(从25~50 nm)。在仿真中,轮流对这两个区域的STI/SOI1界面设置一个8×1012cm-2的电荷密度(Qt),来研究STI中不同区域空穴陷阱电荷对器件性能的影响机制。此处所设置的电荷密度为有效电荷,它包含了氧化层内部及界面处的陷阱电荷。对于其他SiO2/Si界面,电荷密度则设置为0 cm-2。仿真所得到的两种不同陷阱电荷分布下器件的转移特性曲线如图7所示。从图7可看出,对于上述两种陷阱电荷分布,转移特性曲线均出现了“驼峰效应”。但当空穴陷阱电荷分布在STI底部区域时,“驼峰效应”更为明显。这说明STI中空穴陷阱电荷分布的越深,栅极对寄生泄漏电流的控制力越弱,进而在器件沟道中感生出更多的电子。通过对SOI2层施加负的偏置电压,两种陷阱电荷分布下的STI泄漏电流均可得到一定程度的抑制。

图6 TCAD仿真中STI顶部和底部区域定义示意图Fig.6 Schematic diagram of definition of top and bottom areas of STI in TCAD simulation

图7 陷阱电荷分布在STI顶部或底部区域时器件的转移特性曲线Fig.7 ID-VG characteristic curve of device at trap charge distributed in top or bottom region of STI

2.3 辐照过程中负背栅偏置电压对BOX1和STI中陷阱电荷分布的影响机制

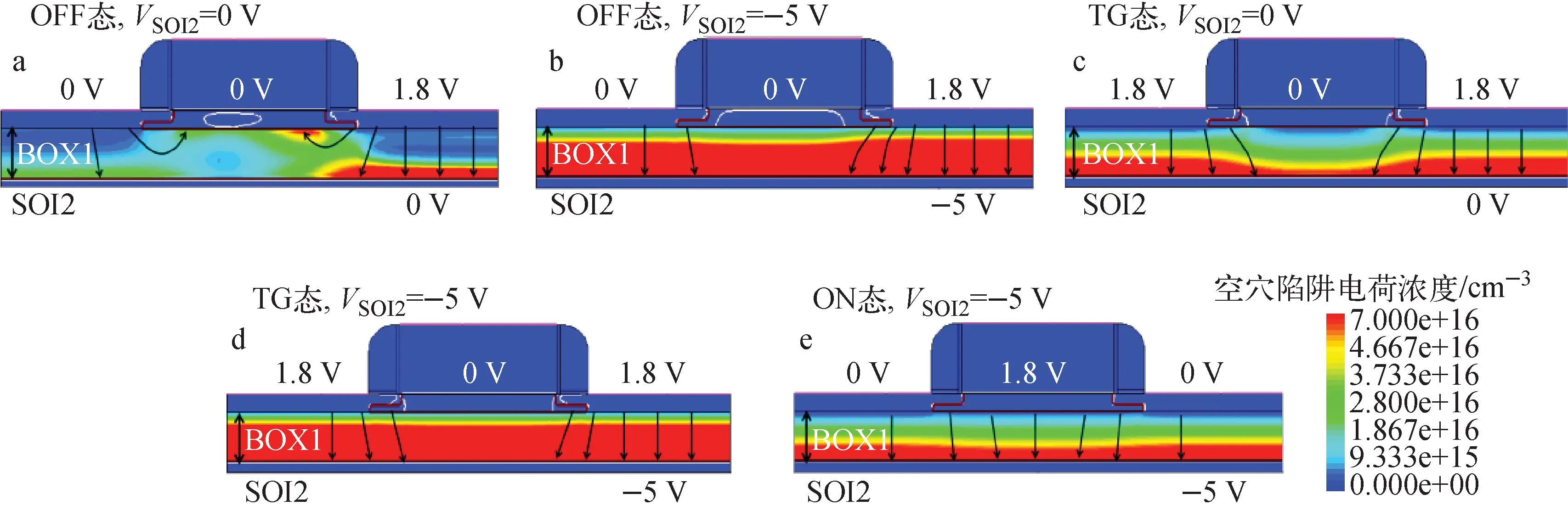

图8、9分别显示了不同辐照偏置条件下,100 krad(Si)总剂量辐照后,CSOI NMOS器件BOX1层和STI中的空穴陷阱电荷浓度分布情况。

图8 100 krad(Si)总剂量辐照后CSOI NMOS器件中BOX1层的空穴陷阱电荷分布及电场线示意图Fig.8 Schematic diagram of hole trap charge distribution and electric field lines in BOX1 layer in CSOI NMOS device after 100 krad(Si) total dose irradiation

对于OFF态偏置,在漏极电场线的作用下,BOX1层中的空穴陷阱电荷主要分布在靠近体区下方的前界面和漏极下方的背界面处(图8a),而STI中的空穴陷阱电荷主要分布在顶部区域(图9a)。100 krad(Si)时,STI/SOI1界面处的空穴陷阱电荷密度为1×1016cm-3,远小于BOX1层前界面处的空穴陷阱电荷密度(7×1016cm-3),且分布在STI顶部区域的空穴陷阱电荷对泄漏电流的影响要更小。因此,在该偏置条件下,背沟道导通是主要的泄漏路径。通过对SOI2层施加负的偏置电压,大多数电场线将会终止于SOI2层,这将导致BOX1层中的空穴陷阱电荷主要在背界面处积累(图8b),进而减弱其对有源区的影响[17],而沟道附近的STI中只会俘获少量空穴电荷(图9b),因此不会产生侧墙漏电。

图9 100 krad(Si)总剂量辐照后CSOI NMOS器件STI中的空穴陷阱电荷分布Fig.9 Hole trap charge distribution in CSOI NMOS device STI after 100 krad (Si) total dose irradiation

对于TG态偏置,浮体电势被源、漏极电势提升至接近1.8 V,在电场线的作用下,空穴陷阱电荷主要分布在BOX1层的背界面附近(图8c),从而导致实验中所观察到的更小的器件性能退化。但与此同时,浮体电势也增大了沟道与STI之间的电势差,使得更多的空穴陷阱电荷分布在STI的顶部区域(图9c)。由于STI顶部区域的空穴陷阱电荷对侧墙漏电的影响较小,因此,在低辐照剂量下不会产生侧墙漏电通道。当VSOI2=-5 V时,负的背栅偏压增加了BOX1层中的电场强度,进而增加了空穴电荷的俘获量(图8d)。这将导致BOX1层前界面沟道下方区域俘获较0 V背偏情况下更多的空穴陷阱电荷,这很好地解释了上述实验中所观察到的现象,即在低辐照剂量下,TG态VSOI2=-5 V偏置晶体管的阈值电压漂移量较TG态VSOI2=0 V偏置晶体管的更大。与此同时,STI顶部区域的空穴陷阱电荷浓度开始降低,转而在BOX1层的背界面处大量积累(图9d)。

对于ON态偏置,由于前栅电压被沟道电子所屏蔽,因此BOX1层中的空穴陷阱电荷分布主要由背栅电压决定。在负背栅偏置电压的作用下,BOX1层中的空穴电荷向背界面移动(图8e),从而减小了其对前栅晶体管的影响。因此,正如实验中所观察到的那样,不会产生背沟漏电。但此时,STI中却存在较强电场,且该电场线的方向指向STI/SOI1界面。因此,STI中的大量空穴陷阱电荷会分布在沟道附近。辐照过程中,在正的前栅电压和负的背栅偏置电压的共同作用下,空穴陷阱电荷会主要积累在STI/SOI1界面的下半部分(图9e),进而引起侧墙漏电。

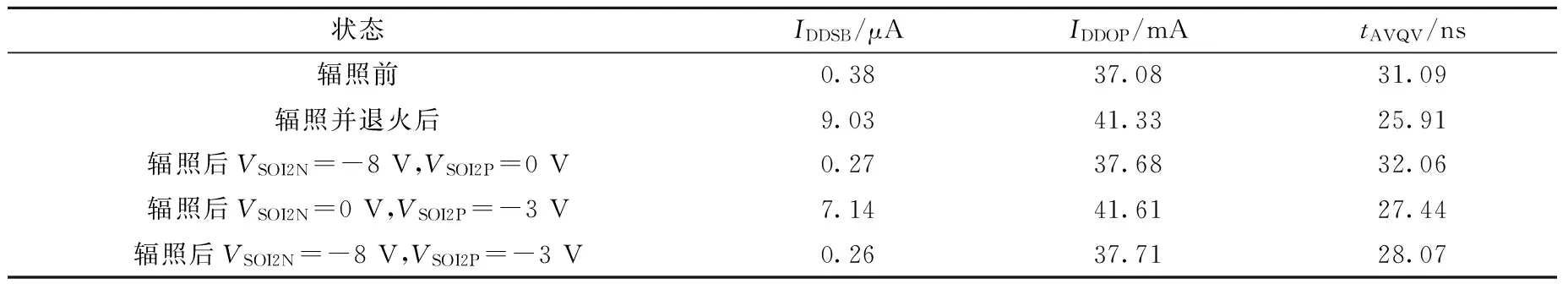

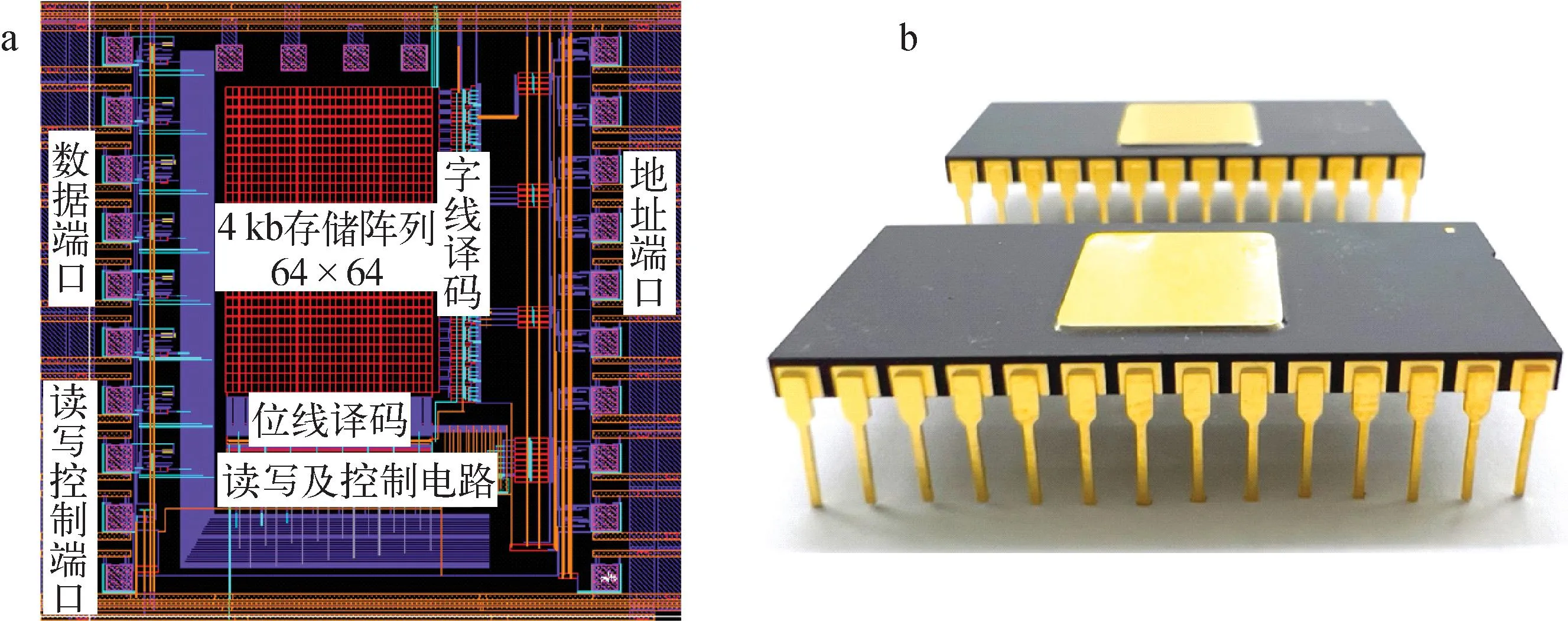

2.4 CSOI SRAM总剂量验证

为评估CSOI电路背偏调控抗总剂量辐照的能力,设计并制备了CSOI 4kb SRAM验证电路。CSOI 4kb SRAM对应的版图和封装图示于图10。总剂量辐照采用北京大学60Co源。在同一批次CSOI工艺SRAM集成电路中,通过功能测试,选取功能正常的3只器件进行总剂量辐照实验,选取1只器件作为对比器件。试验开始时,按剂量率100 rad(Si)/s辐照至2.5 Mrad(Si),背偏施加电压为0 V,然后50 rad(Si)/s辐照至6 Mrad(Si),背偏电压N管为-5 V、P管为0 V,再过辐照3 Mrad(Si),背偏电压N管为-5 V、P管为0 V,最后高温退火,背偏电压N管为-5 V、P管为0 V。该试验方法采用大剂量率加速辐照配合加速退火试验,用较短的时间在地面评估器件在轨实际发生的辐射损伤情况[18],典型试验结果列于表2。由表2可知:1) 试验后3只样品SRAM读写功能均正常,静态电源电流(IDDSB)增加8.65 μA,工作电流(IDDOP)增加4.25 mA,地址存取时间(tAVQV)从31.09 ns变化为25.91 ns。

表2 辐照前后SRAM电参数变化Table 2 Changes in electrical parameters of SRAM before and after irradiation

图10 CSOI 4kb SRAM版图(a)和封装图(b)Fig.10 Layout (a) and packaged (b) maps of CSOI 4kb SRAM

2) 试验后通过NMOS配置层施加负压可有效抑制静态电源电流和工作电流的增加,恢复至辐照前水平;PMOS配置施加偏压对电流增加影响较小。

由上述分析可知,在辐照和测试过程中,对NMOS晶体管施加持续的负背栅偏置电压,能够有效抑制总剂量效应,降低前栅偏置电压对BOX1层中陷阱电荷分布的影响,进而减小电路中不同偏置晶体管总剂量响应差异性,这为采用背偏电压实现总剂量效应加固提供了新的思路。

3 CSOI单粒子效应及加固

本节将分别介绍CSOI器件单粒子效应及背偏调控机理,以及总剂量效应与温度效应对CSOI器件单粒子效应的影响,最后通过CSOI 4kb SRAM的重离子实验验证配置层调控单粒子效应的加固效果。

3.1 CSOI器件单粒子效应机理

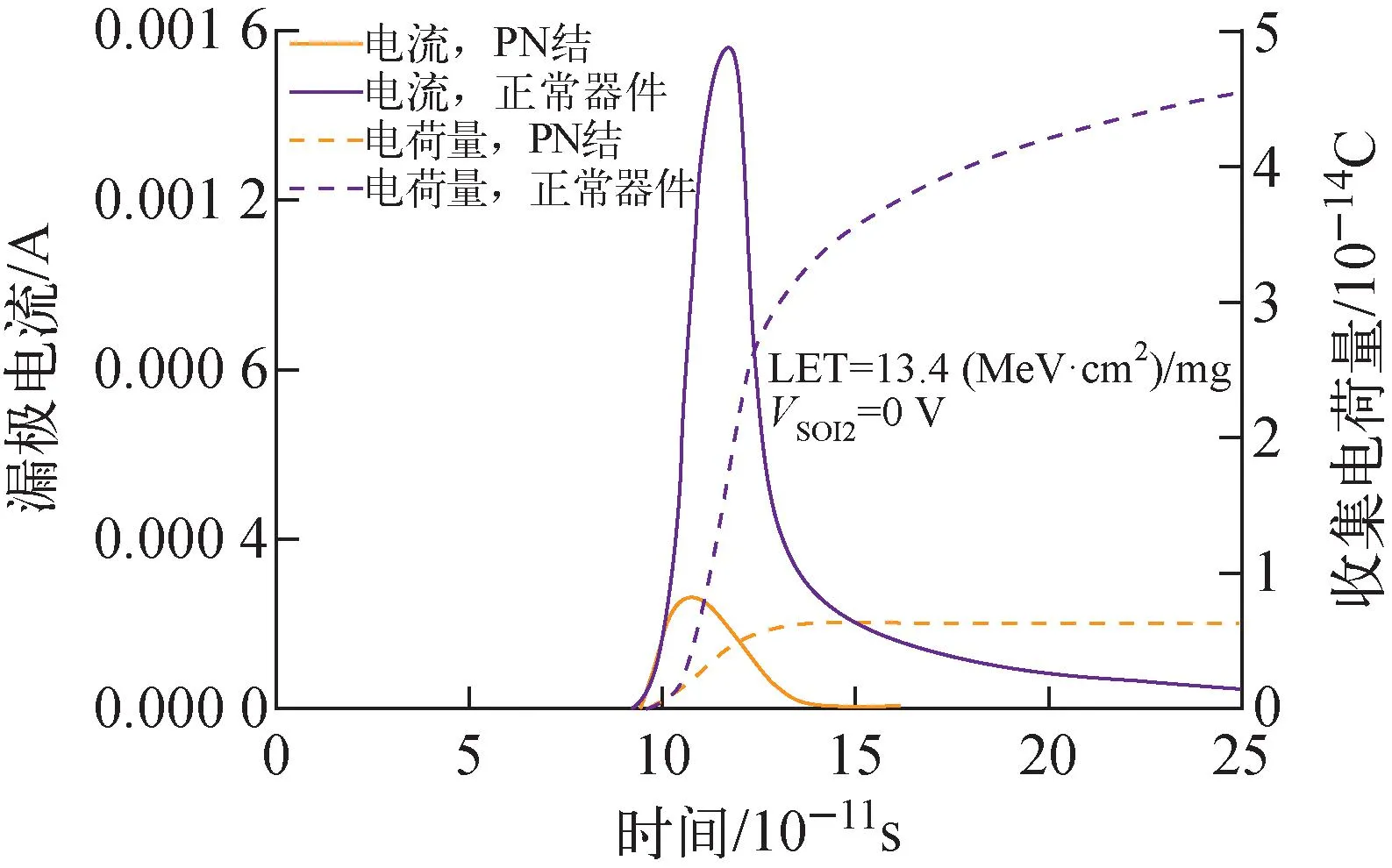

采用TCAD工具建立与实验结果相符的NMOS(图11a)和PN结器件(图11b)模型,仿真发现MOS器件的单粒子收集电荷量远大于PN结器件的收集电荷量(图12),约为7.5倍[19]。由于MOS器件主要的电荷收集机制有漂移运动、扩散运动、寄生双极放大效应,而PN结器件的主要电荷收集机制为漂移运动、扩散运动,这说明寄生双极晶体管放大效应是CSOI器件单粒子离化电荷的主要收集机制。

图11 CSOI MOS(a)和PN结器件(b)TCAD模型Fig.11 Transistor (a) and PN diode (b) TCAD model of CSOI

图12 CSOI NMOS器件与PN结器件单粒子瞬态电流与收集电荷量对比Fig.12 Single-event transient current and collected charge of CSOI device vs. PN diode device

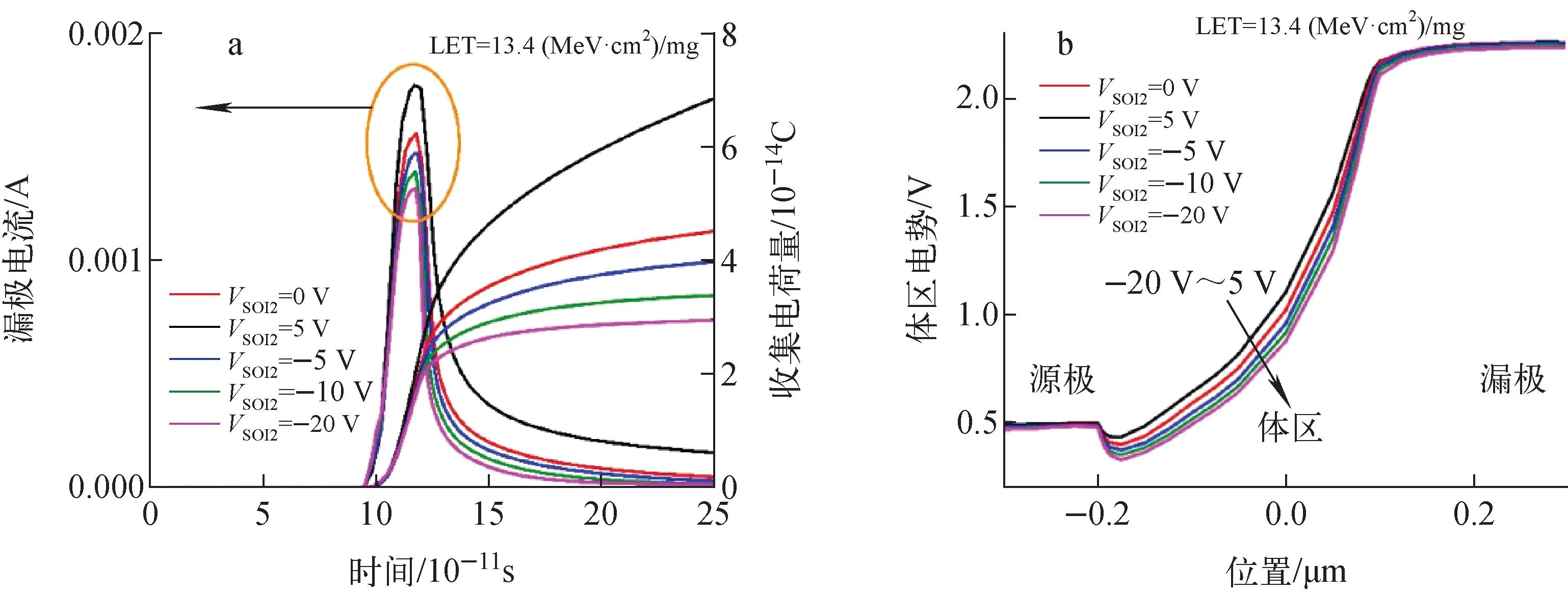

图13a为不同背栅电压下的CSOI NMOS的单粒子瞬态电流,以及对电流积分获得的漏极收集电荷量。可看出,施加正的背栅电压会增大单粒子瞬态电流,增大漏极的收集电荷量;施加负的背栅电压,会降低单粒子瞬态电流,降低漏极收集电荷量。这是因为寄生双极效应是主要的电荷收集机制,通过施加负的背栅电压,可降低体区电势(图13b),进而降低寄生双极效应。其中VSOI2代表仿真过程中对CSOI NMOS施加的背栅电压。这一结论有很高的利用价值,电路设计人员可根据需要在性能、功耗及抗辐射能力方面做出合理的取舍。

图13 不同背栅电压下单粒子瞬态电流(a)和体区电势(b)Fig.13 Single event transient current (a) and body potential (b) changes under different back gate biases

3.2 温度对CSOI单粒子效应的影响

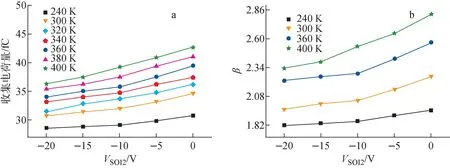

温度同样可能会影响器件单粒子效应的电荷收集,而电荷收集量将直接影响器件的SET敏感性[20-23]。图14为不同背栅电压与温度下的CSOI NMOS单粒子电荷收集量和寄生双极晶体管电流增益变化[19]。随着温度从240 K升高到400 K,CSOI NMOS器件的电荷收集量增大了39%,如图14a所示。温度对CSOI器件电荷收集量增大的原因是温度使CSOI器件寄生双极晶体管放大效应增强。随着温度的升高,CSOI器件寄生双极晶体管电流增益(β)增大,电荷收集量增多。通过在高温环境下,对CSOI施加负的背栅电压,进而降低寄生双极增益,减小敏感节点的收集电荷量(图14b)。

图14 CSOI NMOS单粒子收集电荷量(a)和寄生双极晶体管电流增益(b)Fig.14 Charge collection (a) and parasitic bipolar gain (b) vs. back-gate bias

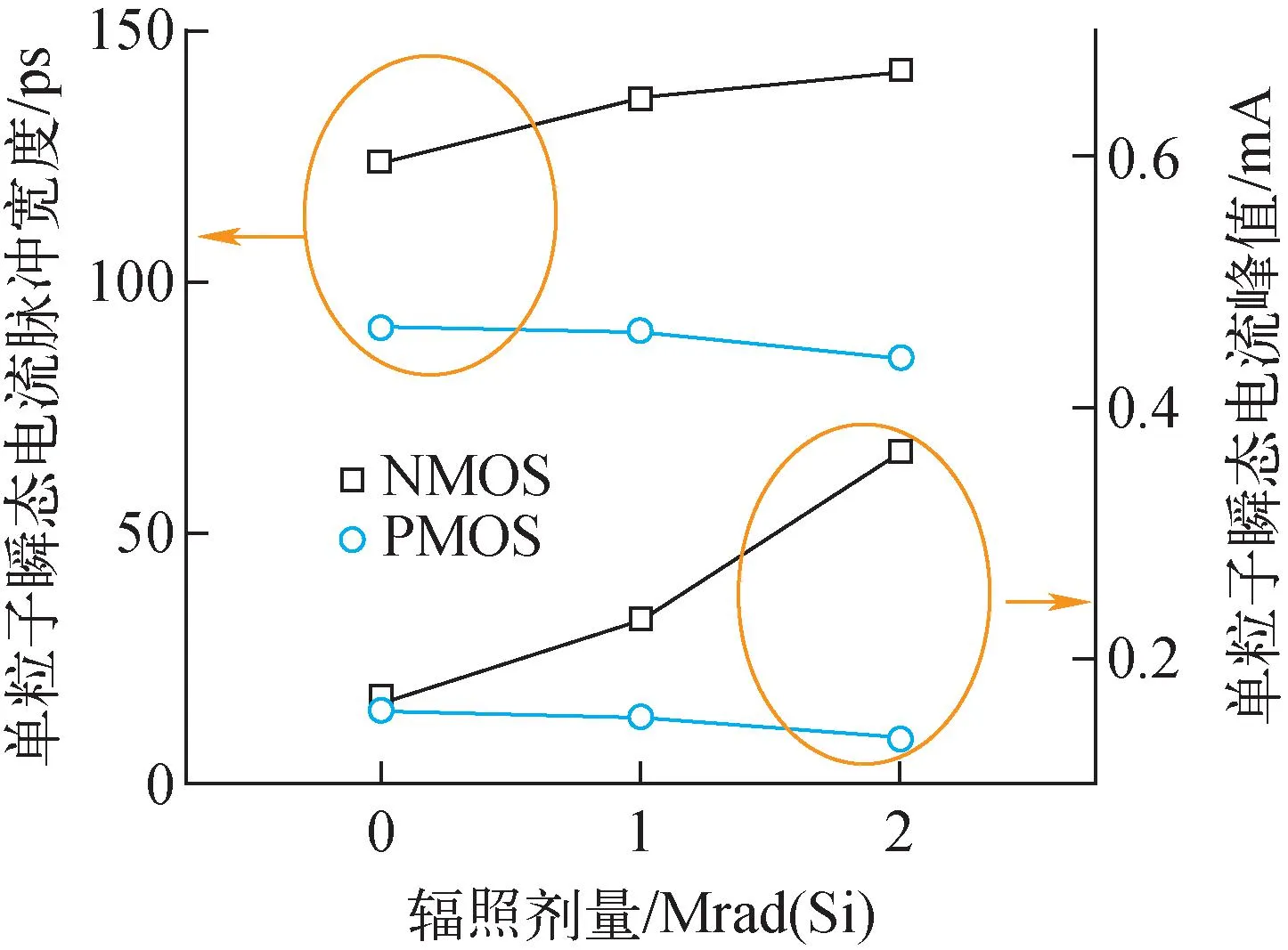

3.3 总剂量辐照对CSOI单粒子效应的影响

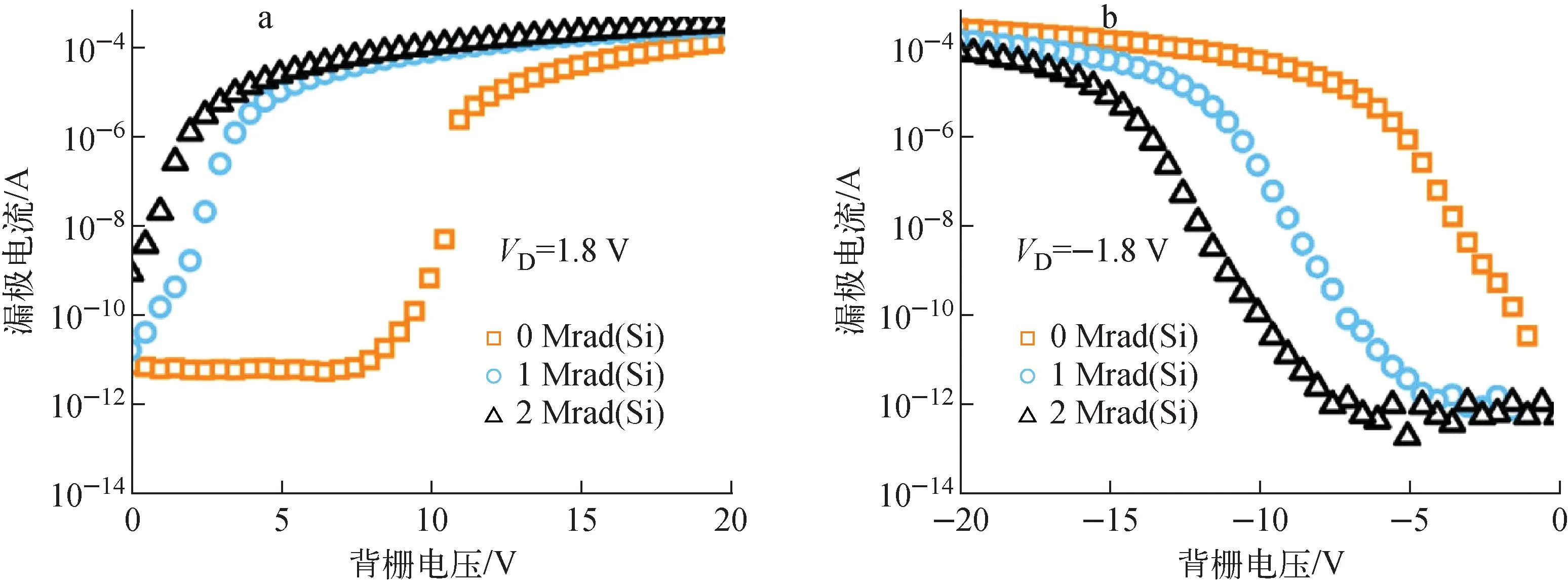

总剂量效应会使得CSOI器件BOX层中积累正电荷,导致背栅阈值电压负漂,如图15所示[24]。对总剂量辐照后的器件进行激光模拟单粒子实验[25]。随着辐照剂量的增大,CSOI NMOS的单粒子瞬态电流峰值与宽度均增大,其中峰值显著增大。CSOI NMOS和PMOS在不同辐照剂量下的单粒子瞬态电流峰值和宽度均值的变化示于图16。对CSOI NMOS施加负背栅电压,不仅补偿了BOX1层中正陷阱电荷,而且抑制了寄生双极晶体管放大效应,进而降低了单粒子瞬态电流峰值(图17a)。TCAD仿真发现,这是因为总剂量辐照在BOX1层中产生的正陷阱电荷,增大了体区的电势,导致寄生双极晶体管放大效应增强。通过施加负背栅可以降低BOX层中正陷阱电荷导致的体区-源区势垒增大,导致寄生晶体管开启变得更加困难,如图17b所示。

图15 CSOI NMOS(a)和PMOS(b)背栅输出特性曲线随辐照剂量的变化Fig.15 Experimental results with back-channel ID-VSOI2 characteristics of CSOI NMOS (a) and PMOS (b) before and after γ radiation

图16 CSOI NMOS和PMOS在不同辐照剂量下的单粒子瞬态电流峰值和宽度均值Fig.16 Average SET peak and SET FWHM at different radiation doses of CSOI NMOS and PMOS

图17 CSOI NMOS单粒子瞬态电流峰值随背栅电压和辐照剂量的变化(a)及体区电势随背栅电压与BOX层陷阱电荷的变化(b)Fig.17 Average SET peak at different VSOI2N and different radiation doses (a) and electrostatic potential of body along channel before ion strikes at different VSOI2N and QBOX1 (b) for CSOI NMOS

以上研究结果为CSOI器件及电路在空间综合辐射环境中协同效应的加固提供了重要的技术途径。

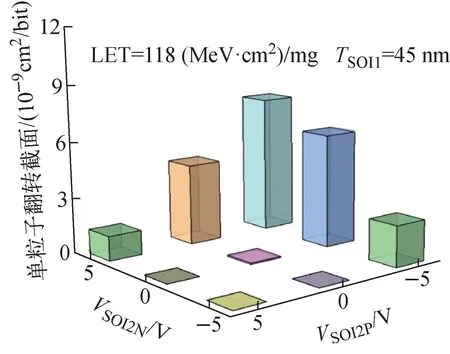

3.4 CSOI SRAM单粒子验证

为了评估CSOI电路背偏调控抗单粒子辐照的能力,使用研制的CSOI 4kb SRAM在哈尔滨工业大学空间环境地面模拟装置(SESRI)进行了重离子辐照实验。所有待测电路存储阵列填充数据图形均为55AAh。单粒子翻转效应测试时,将待测器件的电压拉低10%,即电源供电1.62 V。单粒子锁定效应测试时,将待测器件的电压拉高10%,即电源供电1.98 V。通过重离子实验研究了CSOI SRAM在不同背栅下的单粒子翻转情况,提出了一种可降低单粒子翻转和功耗而不改变电路性能的背栅调控策略。该配置层调控策略在不影响电路功耗的前提下,大幅提升了SRAM的抗单粒子翻转的能力。在线性能量转移(LET)高达118 (MeV·cm2)/mg的情况下,通过施加背栅可实现无SEU翻转(图18)。

图18 不同背栅电压下SRAM电路的翻转截面Fig.18 SEU cross sections of SRAM circuit at different back-gate biases

4 结论

本文详细描述了一种新型可配置SOI器件技术,通过在配置层施加偏置电压,实现对器件性能和抗辐照能力的调控。与传统SOI技术相比,CSOI技术配置层调控的范围更大、粒度更小,不仅有效提高器件和电路的抗辐照能力,而且提高了电路设计的灵活性。总剂量实验和仿真证明,对CSOI NMOS施加负偏置电压,补偿了BOX1中辐照诱生正陷阱电荷引起的器件性能退化。而单粒子的效应的加固主要通过抑制寄生晶体管双极放大效应实现。温度和总剂量辐照均恶化了CSOI器件的单粒子瞬态电流,但配置层偏置加固仍然有效。CSOI SRAM的总剂量和重离子实验证实了一种最优的配置层策略,可有效提高电路的抗总剂量和单粒子水平,其中抗总剂量能力达到6 Mrad(Si)、单粒子翻转阈值大于118 (MeV·cm2)/mg。CSOI技术的高抗辐照保障水平,在以木星为代表的深空探测、核应急装备的电子系统具有广阔应用前景。

感谢合作单位北京大学、哈尔滨工业大学、上海新傲科技股份有限公司、中国科学院上海微系统与信息技术研究所对本研究的鼎力支持。