JFET区宽度对SiC MOSFET单粒子效应的影响

许明康,贾云鹏,*,周新田,胡冬青,吴 郁,唐 蕴,黎荣佳,赵元富,,王 亮

(1.北京工业大学 信息学部,北京 100124;2.北京微电子技术研究所,北京 100076)

随着功率器件朝着高功率密度、高工作频率和低损耗方向不断发展,传统硅(Si)基器件在设计和工艺方面已趋于成熟,并接近所谓的“硅极限”[1]。在不断增长的功率半导体产业需求下,迫切需要开发高性能的新型功率半导体器件,因此第三代宽禁带半导体材料应运而生,其中以碳化硅(SiC)和氮化镓(GaN)材料的应用最为广泛。SiC功率器件在光伏产业、家电、铁路运输、电力配送等多领域有广泛应用,并在新能源汽车逐渐崛起的未来具备巨大的开发潜力[2-6]。

SiC具有优越的电学和热学性能,如导热系数大、化学性能基本稳定、击穿电场强度大、电子饱和速率高以及高抗辐射性等特性,已成为新一代取代Si材料的半导体材料。20世纪90年代后期以来,SiC MOSFET(金属-氧化物半导体场效应晶体管)器件迅速发展[7-12]。SiC MOSFET因其耐高温、低损耗、开关速度快和阻断电压高等出色特性,成为高压、高温、强辐射和高频开关领域的首选之一,也在航空航天系统电源电路中扮演不可或缺的角色。然而,SiC器件的抗单粒子效应能力较弱,其单粒子敏感性和复杂程度与理论预期存在较大差距,容易发生漏电退化甚至烧毁失效[13-17]。

国外对SiC MOSFET的单粒子效应已进行了深入研究。2017年,Ali等[18]研究了用于抗辐射空间应用的600 V Si-on-SiC LDMOS(横向双扩散金属氧化物半导体场效应晶体管)的单粒子效应和总电离剂量。2019年,Ball[19]研究了SiC MOSFET的中子诱发SEB的横截面和时间速率失效。2020年,Martinella等[20]提出了SiC MOSFET单粒子失效的3个阶段:电荷收集、漏电退化和单粒子烧毁。2021年,Martinella[21]又用PIGS(辐照后栅应力测试)证实了漏电退化阶段氧化层的潜在损伤。

近年来,我国也在SiC MOSFET器件的单粒子效应方面进行了研究。如空军工程大学的刘忠永等[22]对SiC中的同素异形体4H-SiC和6H-SiC的横向双扩散金属氧化物半导体场效应晶体管(VDMOS)以及4H-SiC半超结VDMOS进行了单粒子烧毁(SEB)研究。通过对栅氧化层的研究,给出了一种了“高K栅”介质HfO2加固结构。

本文拟通过实验与仿真,探究JFET区宽度这一重要参数对SiC MOSFET单粒子效应的影响,探索其内部机理,根据机理解释器件在单粒子辐照实验时,JFET区宽度的变化会引起器件内部哪些参数的改变,从而判断其影响的两面性,为今后对SiC MOSFET进行抗辐加固提供理论基础。

1 单粒子辐照实验

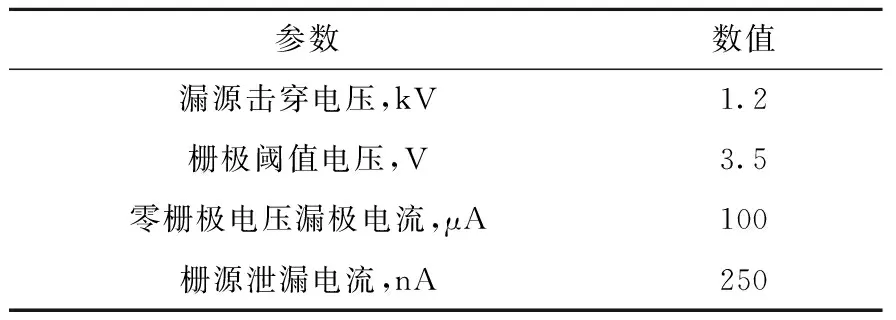

本实验以JFET区宽度为1.6 μm和2.0 μm的两种1.2 kV SiC MOSFET为样品(分别记为A器件、B器件)。辐照前所有样品均进行开帽,去除芯片表面的防护胶,以减少入射离子达到芯片敏感区域的能量损失。样品的最大电参数如表1所列。

表1 样品的最大电参数Table 1 Maximum electrical parameters of samples

单粒子辐照实验在中国科学院近代物理研究所的重离子加速器上进行。离子束流窗口面积为2.2 cm×2.2 cm,所有实验在非真空室温条件下进行。离子种类为181Ta35+离子,以垂直方式入射,其在SiC中的射程为79.29 μm,在实验中可以穿透整个外延层。其他实验参数如表2所列。

表2 实验参数Table 2 Test parameters

本文所用实验装置如图1所示,该装置一次可装载约22颗样品(以常规的金封MOSFET样品为例),实验过程如下:完成一颗样品辐照后,系统自动通过夹具的横向运动将下一颗样品对准测试窗口,同时更换预设的样品测试程序,完成该样品的测试。通过此系统对高压源表(Keithley2410和Keithley2400)进行控制,施加漏极与栅极的偏置电压,并对漏极电流和栅极电流进行实时监控。

图1 单粒子效应实验装置Fig.1 Single event effect experiment setup

2 结果与讨论

2.1 器件单粒子漏电退化和烧毁

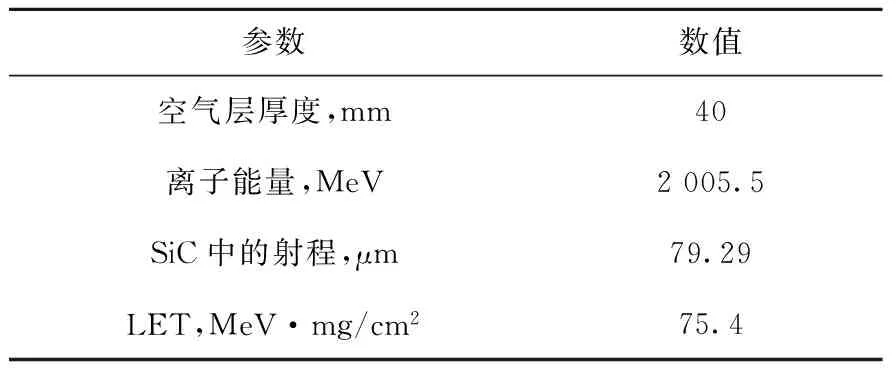

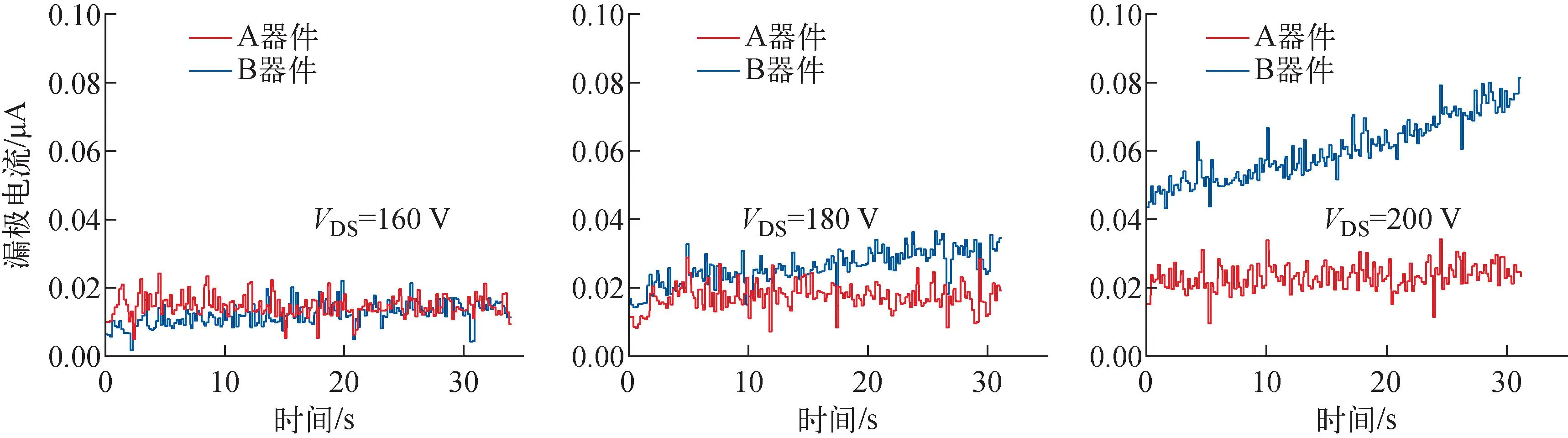

辐照过程中,栅极电压(VGS)设为0 V,使器件处于关闭状态,漏极电压(VDS)每档均设为恒定正值。使用不同的漏极电压(从80 V逐级增加,每增加20 V设为一档),寻找器件发生漏电退化和烧毁的电压等级。随着漏极电压的增大,漏极电流(IDS)与栅极电流(IGS)也不断增加,直至两类器件均发生严重漏电退化停止实验。每个电压等级下,入射离子总注量均设为3×105cm-2。不同漏极电压下电流随时间的变化如图2所示。

图2 不同漏极电压下电流随时间的变化Fig.2 Variation of current over time under different drain voltages

在漏极电压较小时,漏极电流在10 nA以下,电源采集数值受单粒子效应实验环境影响,故在指数条件下忽略10 nA以下的值。从图2可看出,160 V时,器件漏极电流明显增大。漏极电流随漏极电压的增大而增加。同时每个电压档下,B器件漏极电流明显大于A器件,说明A器件的抗单粒子效应能力更好。400 V时,器件发生明显烧毁。

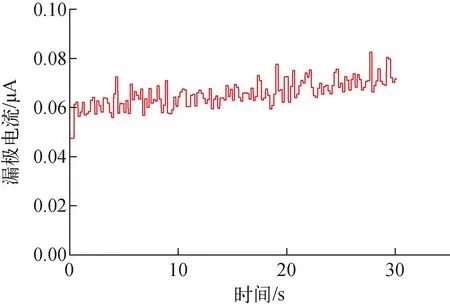

为更好地显示A器件和B器件漏电退化起始点的差距,从图2的多组漏极电压中选取A器件和B器件漏电退化、发生轻微漏电退化和发生明显漏电退化的3个漏极电压进行单粒子辐照,其电流随时间的变化示于图3。由图3可看出,漏极电压为160 V时,A器件和B器件漏极电流基本不随时间而变化,稳定在15 nA左右。漏极电压为180 V时,B器件发生了轻微漏电退化,漏电流从20 nA逐渐增大至35 nA,而A器件电流基本稳定。漏极电压为200 V时,B器件发生明显的漏电退化,漏电流从50 nA逐渐增加至80 nA,可以认为漏极电压为200 V时发生了漏电退化,而A器件漏极电流仍稳定在约25 nA。为考察A器件发生漏电退化的漏极电压,将漏极电压增加至220 V,此条件下漏极电流随时间的变化如图4所示,可见漏极电压为220 V时A器件发生漏电退化,漏极电流从55 nA逐渐增加至70 nA。综上所述,A器件的单粒子漏电退化起始电压远大于B器件,说明A器件具有更好的抗单粒子效应能力。

图3 A、B两器件不同漏极电压下漏极电流随时间的变化Fig.3 Variation of drain current over time for A and B devices at different biases

图4 A器件在VDS=220 V下漏极电流随时间的变化Fig.4 Variation of drain current over time for A device at VDS=220 V

由图2可知,器件在400 V发生烧毁。故将A、B两器件漏极电压增大至400 V进行单粒子辐照实验,结果如图5所示。由图5可见,粒子束流开始后,A、B两器件漏极电流瞬间达到限流,发生单粒子烧毁,说明A、B两器件的单粒子烧毁阈值均为400 V。

图5 A、B器件在400 V下发生烧毁时电流随时间的变化Fig.5 Variation of current over time for A and B devices during burnout occurrence at 400 V

由以上实验数据可知,在单粒子效应实验中,较低电压下,A、B两器件均会出现典型的单粒子漏电退化现象,B器件的漏电退化起始电压更小,说明JFET区宽度大更易发生漏电退化。而在较大电压下,两器件几乎同时发生单粒子烧毁。表明JFET区宽度对单粒子烧毁电压的影响并不大。

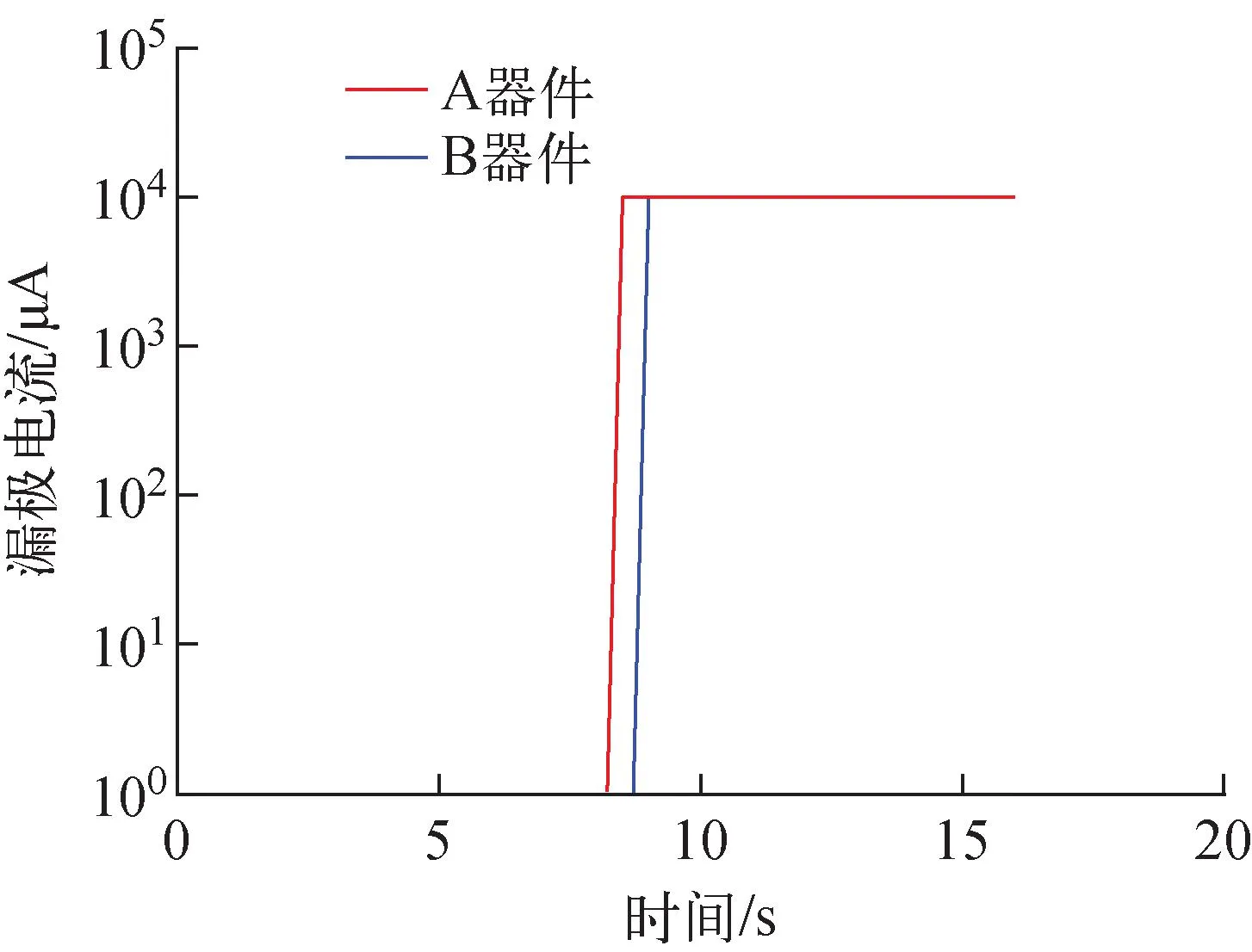

2.2 负栅压下器件单粒子的漏电退化

辐照过程中,栅极电压设为-5 V,使器件处于关闭状态,漏极电压为恒定正值。漏极电压从80 V开始逐级增加,每级增加20 V,直至两器件均发生严重漏电退化停止实验。每个电压等级下,入射离子总注量设为3×105cm-2。

观察器件栅极电压设为-5 V下的实验数据发现,器件的漏电流主要通过栅极泄漏,栅极的泄漏电流大于漏极,选取栅极漏电流作为漏电退化的依据进行比较。栅极电压设为-5 V,A、B两器件在不同偏压下栅极电流随时间的变化示于图6。从图6可看出,VDS=160 V时,A、B两器件均已有较大的栅极泄漏电流,A器件的漏电流几乎不随时间变化,B器件发生了轻微的漏电退化。VDS=180 V时,A、B两器件均发生较明显的漏电退化。VDS=200 V时,A、B器件均发生严重的漏电退化。

图6 A、B器件不同偏压下栅极电流随时间的变化Fig.6 Variation of gate-source current over time for A and B devices at different biases

由以上结果可知,施加-5 V栅极电压较不加栅极反偏电压时更易发生漏电退化。A器件较B器件发生漏电退化的起始点更晚,且漏电明显小于B器件,但漏电退化起始点的差距与不加栅极反偏电压时相比更小,表明JFET区宽度在对器件施加栅极反偏电压时仍对其漏电退化有影响,但由于栅极反偏电压的作用,影响程度较不加栅极偏压时有所减小。

3 单粒子效应机理仿真

3.1 单粒子漏电退化拟合仿真

Sentaurus TCAD是美国Synopsys公司开发的一款用于半导体器件模拟和工艺设计的软件,广泛应用于半导体工业中,主要用于设计、优化和分析各种半导体器件和工艺,以改进性能和可靠性。该软件涵盖了多个模块和算法,可用于半导体器件的物理建模、仿真和分析。为更好地了解不加栅压和施加负栅压下JFET区宽度对器件单粒子漏电退化的影响机理,本文使用Sentaurus TCAD对实验所用的两组器件进行仿真。

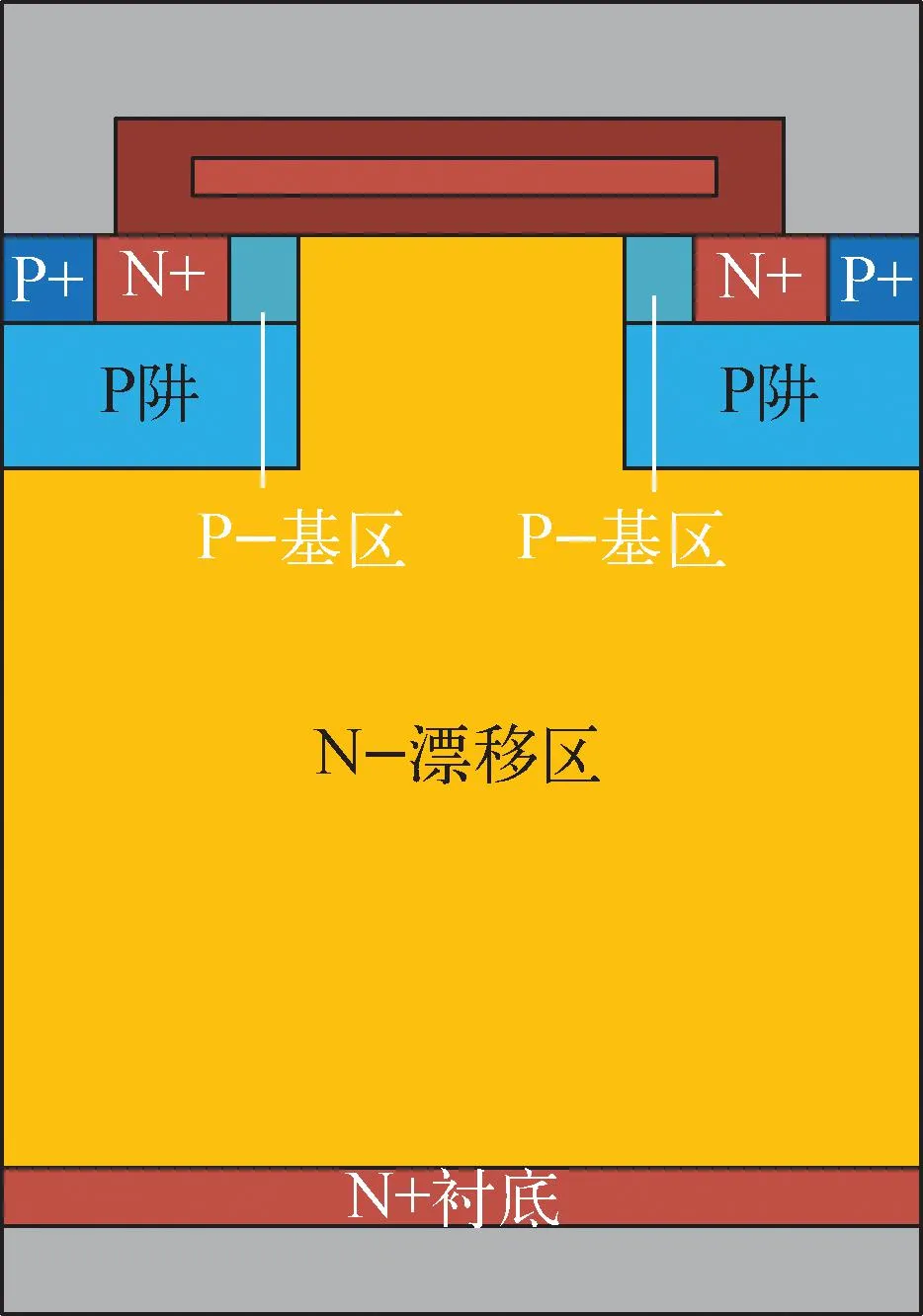

平面栅SiC MOSFET的结构如图7所示[23]。为准确仿真被测器件的单粒子效应,对被测器件进行解剖分析,使用SEM获取被测器件内部元胞的详细结构参数。单元胞宽度为6 μm,外延层N-漂移区厚度为10 μm,衬底厚度为300 μm,栅极氧化层厚度为70 nm。通过选择合适的各部分掺杂浓度,对仿真器件与实验器件的电学性能参数进行拟合。

图7 平面栅SiC MOSFET结构示意图Fig.7 Schematic diagram of planar gate SiC MOSFET structure

仿真中重离子轰击位置为器件中央,以便有效观察氧化层电场的变化[24],离子轨迹贯穿整个器件,t为时间参数。

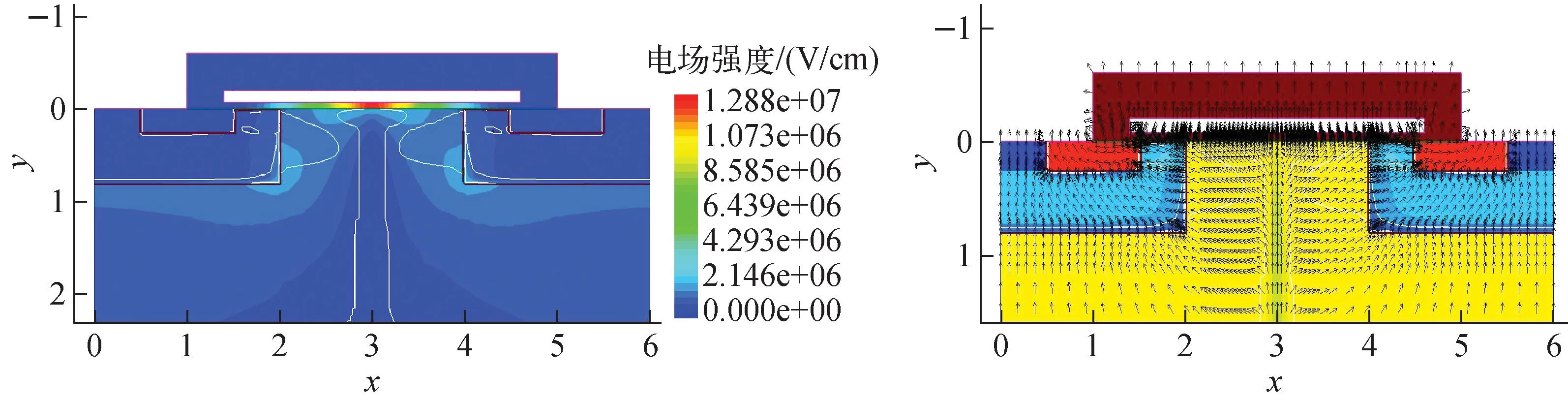

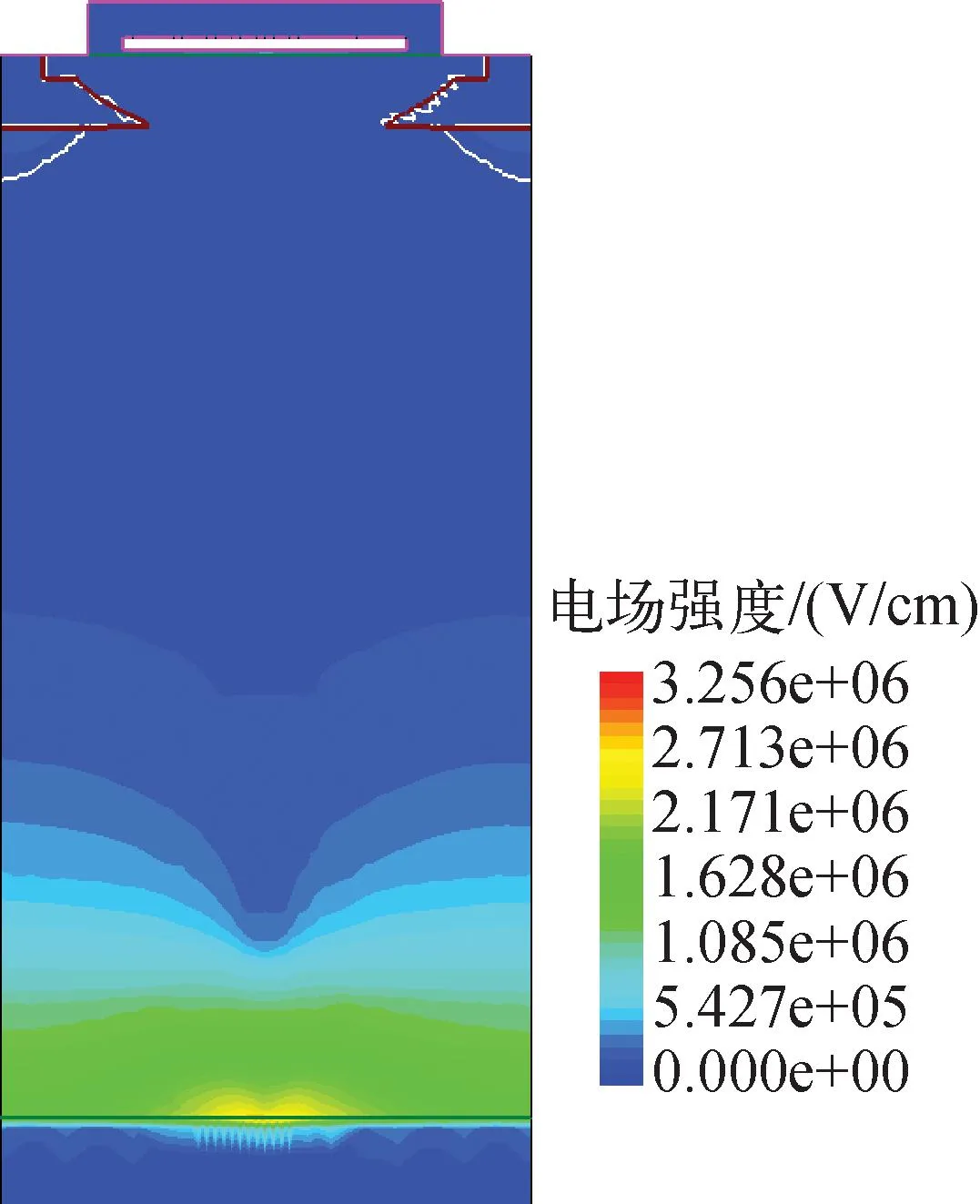

通过对A、B器件的仿真,可以观察到最大氧化层电场出现在重离子轰击的器件中央,在栅氧化层出现了大量电流通路。VDS=200 V、A、B器件的t=4 ps时,器件的电场和电流密度分布如图8所示。

图8 VDS=200 V、t=4 ps下的电场(a)和电流密度(b)分布Fig.8 Electric field (a) and current density (b) distribution at VDS=200 V and t=4 ps

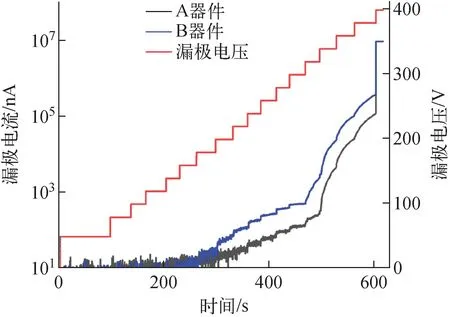

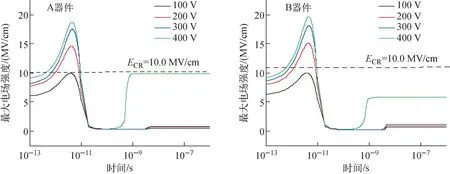

A、B器件氧化层最大电场随时间变化的仿真结果如图9所示。从图9可看出,最大电场强度在t=4 ps时达到最大。此时,离子轰击处SiC和SiO2的界面聚集了大量空穴,从而产生瞬态电场,随后界面下方的空穴通过P-基区向源极泄漏,氧化层电场逐渐减小,并恢复至轰击前的状态。VDS=400 V时已发生单粒子烧毁故无法恢复。器件在VDS=200 V时最大电场强度大于临界电场强度,栅氧化层发生损伤。

图9 氧化层最大电场强度随时间的变化Fig.9 Variation of maximum electric field strength in oxide layer over time

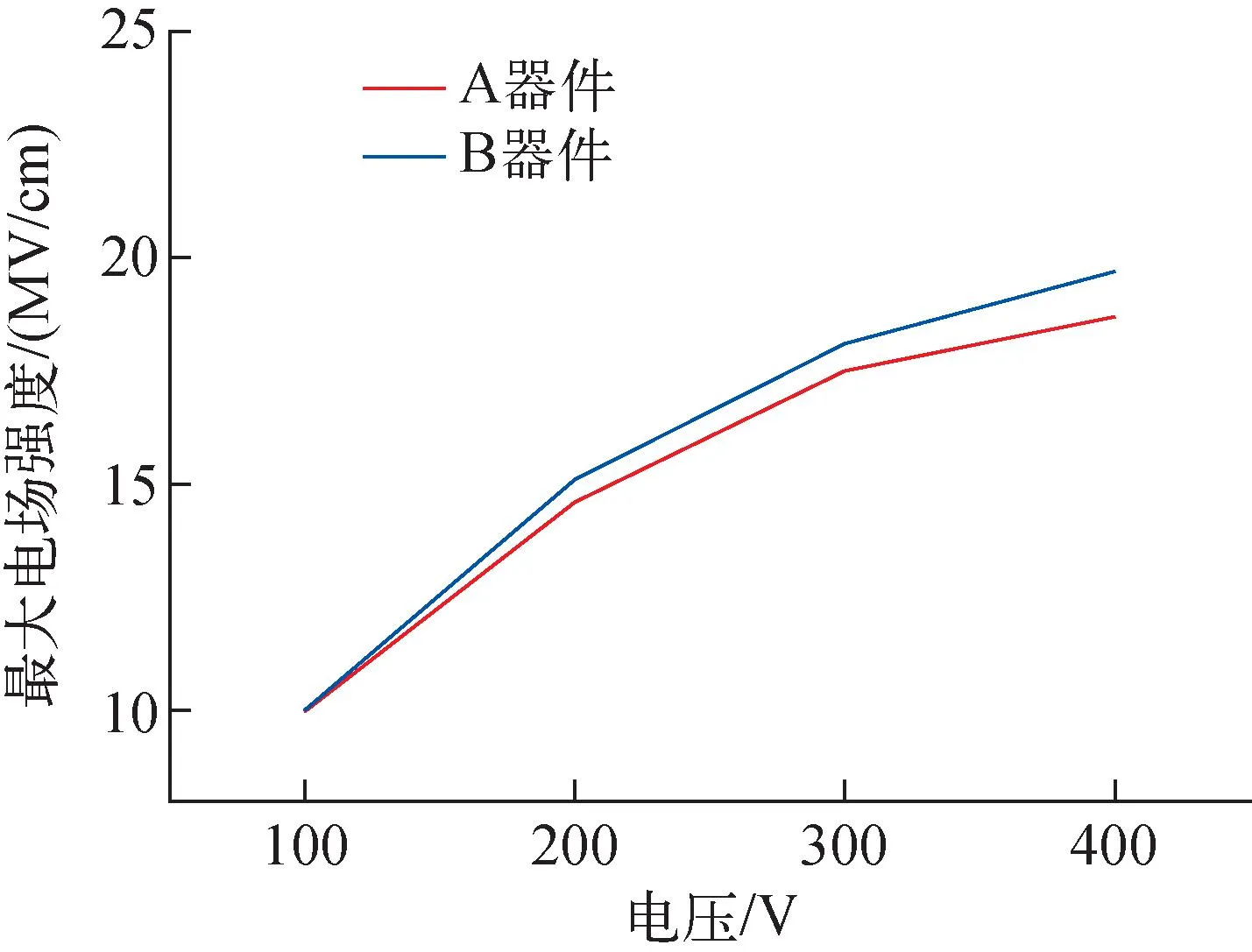

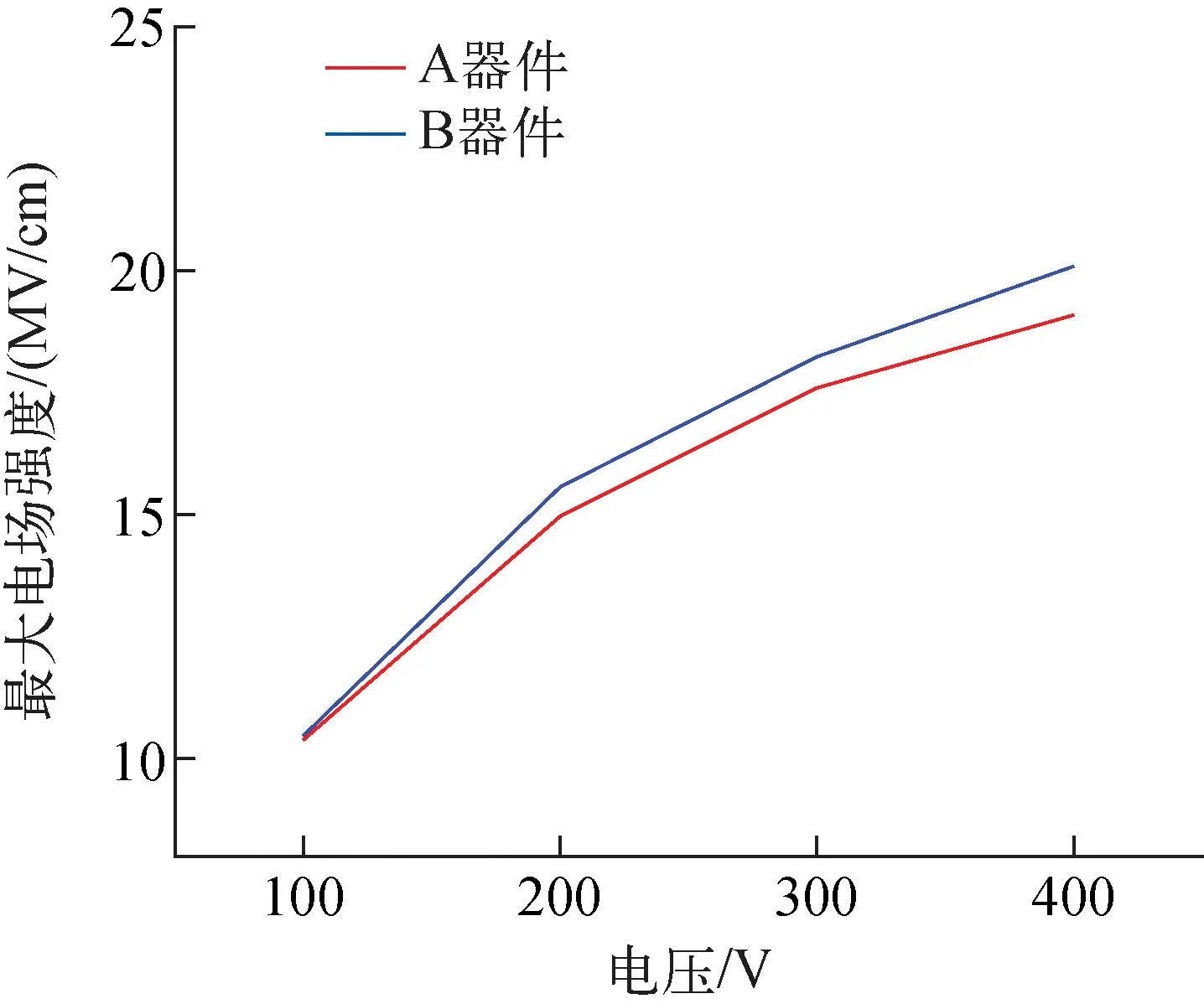

A、B器件氧化层最大电场随漏极电压的变化如图10所示。从图10可观察到:4个漏极电压下,B器件的最大氧化层电场均大于A器件,说明JFET区宽度会影响单粒子轰击时JFET区的空穴积累,从而影响氧化层的电场强度;B器件JFET区宽度大,不利于氧化层下空穴的抽取,导致同一时刻空穴密度更大,氧化层电场强度更大,更易发生漏电退化。

图10 不同漏极电压时A、B器件氧化层最大电场强度对比Fig.10 Comparison of maximum electric field strength in oxide layer of A and B devices at different drain bias voltages

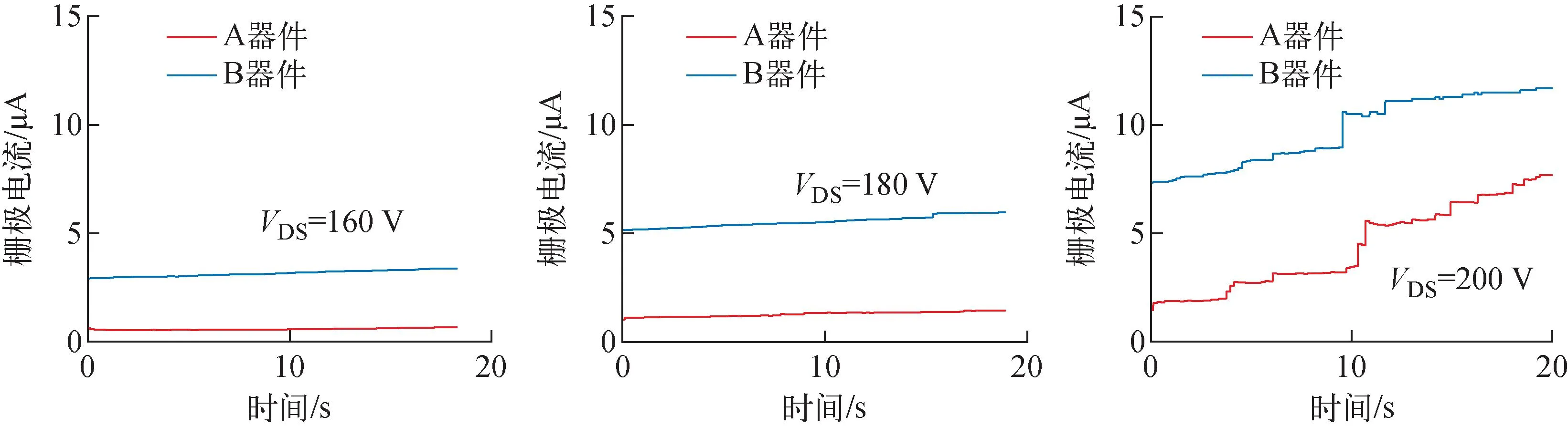

3.2 单粒子烧毁和负栅压下漏电退化拟合仿真

为更好地阐释单粒子烧毁电压与JFET区宽度的关系以及更好地解释施加负栅压对器件漏电退化的影响,分别对烧毁电压和负栅压下的器件进行仿真,其中VDS=400 V、A器件t=0.1 ns下的电场分布如图11所示,-5 V栅极电压下氧化层最大电场强度随漏极电压的变化如图12所示。可以看到,此时电场主要聚集在N+缓冲层和N-漂移区界面处,这是由离子碰撞电离所引起的局部化的能量脉冲所致,随后发生雪崩倍增,产生大量焦耳热,导致器件发生永久性结构损伤。烧毁机理与SiC二极管一致,整个烧毁过程与JFET区宽度相关性不大,所以JFET区宽度的改变并不会对烧毁电压产生太大影响。

图11 VDS=400 V、A器件t=0.1 ns时的电场分布Fig.11 Electric field distribution at t=0.1 ns for A device at VDS=400 V

图12 -5 V栅压下氧化层最大电场强度随漏极电压的变化Fig.12 Variation of maximum electric field strength of oxide layer with drain bias voltage under -5 V bias voltage

-5 V栅压下A、B器件氧化层最大电场随漏极电压的变化如图12所示。由图12可见,给器件施加-5 V栅压后,每一漏极电压下最大氧化层电场强度增加约0.5 MV/cm,这会使得器件漏电退化阈值电压更低。这是由于负栅压下的器件,栅氧化层上多晶硅的一侧电势较JFET区电势低,重离子入射后会有更多的空穴堆积在JFET区,导致氧化层的电场强度更大,栅氧化层更易发生损坏,使得器件更易发生漏电退化。

4 结论

通过对SiC MOSFET设计中的重要参数——JFET区宽度对单粒子效应影响的实验研究,得到如下结论。

1) JFET区宽度的减小有利于提升漏电退化阈值电压,提高器件的抗单粒子效应能力,但对单粒子烧毁电压影响不大。

2) 在施加负栅压的条件下,漏电退化阈值电压明显减小。

3) Sentaurus TCAD仿真结果显示,当漏极电压低于漏电退化阈值电压时,栅氧化层下方的JFET区内会发生空穴积累,对栅氧化层造成损伤,从漏极到栅极形成电流泄漏路径,减小JFET区宽度可以有效改善空穴的抽取速度,减少空穴的积累,提升退化阈值电压。高于漏电退化阈值电压,会对MOSFET造成更严重的损坏,在漏极-源极之间产生电流泄漏路径,并最终导致器件发生单粒子烧毁。在负栅压下,JFET区宽度小的器件,漏电退化阈值也小,但漏电退化起始点的差距较不加栅极反偏电压时小,主要是由于负栅压对栅氧化层下空穴积累的影响作用更强,占更主导的地位。

后续将以此理论为基础,形成更有效的SiC MOSFET抗单粒子效应加固结构。